IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES

# 3-Way Doherty Power Amplifiers: Design Guidelines and MMIC Implementation at 28 GHz

Anna Piacibello<sup>®</sup>, *Member, IEEE*, Vittorio Camarchia<sup>®</sup>, *Senior Member, IEEE*, Paolo Colantonio<sup>®</sup>, *Senior Member, IEEE*, and Rocco Giofrè<sup>®</sup>, *Senior Member, IEEE*

Abstract—This article presents the design strategy and the implementation of a three-way Doherty power amplifier (DPA3W) to enhance the efficiency at deep power back-off. Theoretical design equations are derived, based on which design charts are drawn to explore the available design space, accounting for practical constraints related to the available technology and selected application. The proposed design strategy is demonstrated by the design, fabrication and experimental characterization of a three-way multistage Doherty amplifier optimized for efficiency peaks at 6 and 12 dB back-off. The amplifier is realized on the WIN Semiconductors 150 nm GaN-SiC high-electron-mobility transistor (HEMT) monolithic process at 28 GHz, targeting 5G applications. The prototype achieves saturated output power in excess of 34 dBm and power added efficiency of the order of 15% from 6 to 12 dB back-off, demonstrating competitive performance and a good agreement between simulations and measurements, thus validating the approach.

*Index Terms*—Back-off, Doherty, 5G, GaN, high efficiency, monolithic microwave integrated circuit (MMIC), power amplifiers (PAs).

## I. INTRODUCTION

THE demand for high capacity of future communication systems forces the adoption of advanced modulation schemes with non-constant envelope and very large peakto-average-power-ratio (PAPR). This has a strong impact on the transmitter architecture, especially on the power amplifier (PA), which operates in back-off, i.e., at an average power significantly lower than its saturated one.

At sub-6 GHz communication frequencies, different design strategies have been proposed to maintain also in back-off a reasonably high PA efficiency, the most popular one being presently the Doherty PA (DPA) [1], [2], [3], thanks to its relatively simple and robust design, and its good performance in terms of efficiency and linearity over bandwidths compatible with today's standard requirements. Different metrics are currently in use to specify the linearity requirements of the PAs,

Manuscript received 19 July 2022; revised 16 October 2022; accepted 15 November 2022. This work was supported by the Italian Ministry of University and Research (MUR) through the Progetto di Ricerca di Rilevante Interesse Nazionale (PRIN) 2017 Project under Grant 2017FL8C9N. (*Corresponding author: Anna Piacibello.*)

Anna Piacibello and Vittorio Camarchia are with the Department of Electronics and Telecommunications, Politecnico di Torino, 10129 Turin, Italy (e-mail: anna.piacibello@polito.it).

Paolo Colantonio and Rocco Giofrè are with the Department of Electronic Engineering, University of Rome Tor Vergata, 00133 Rome, Italy (e-mail: giofr@ing.uniroma2.it).

Color versions of one or more figures in this article are available at https://doi.org/10.1109/TMTT.2022.3225316.

Digital Object Identifier 10.1109/TMTT.2022.3225316

noise-to-power ratio (NPR) [4] becoming increasingly popular for satellite communications, whereas adjacent channel power ratio (ACPR) and error vector magnitude (EVM) being among the most used for ground communications.

However, 5G applications and beyond would soon require the PA to manage signals with increasing PAPR (9–12 dB), well beyond the classical 6-dB high-efficiency region of standard DPAs. Crest Factor Reduction can be applied, although at the expense of increased complexity and worse linearity [5]. Therefore, architectures to enhance the efficiency at deep power back-off, such as the *N*-stage and *N*-way DPA [6], [7], [8], [9], [10], [11], the distributed efficient PA (DEPA) [12], [13], and the sequential-load modulated balanced amplifier (S-LMBA) [14], [15], [16], [17], have been developed.

The DPA and S-LMBA architectures typically rely on a limited number of active devices (usually three, one for the Main and two for the Auxiliary), but they are particularly affected by a strong gain penalty, due to the asymmetric input power splitting and the class-C bias point adopted for the Auxiliary devices [6], [9], [17]. Optimized operations in terms of achievable gain and efficiency are possible but require multi-RF-inputs [7], [10]. On the other side, the DEPA has a somewhat limited gain penalty but needs an increasingly high number of active devices to optimize the efficiency at a deeper output power back-off (OBO) [12], [13]. In addition, the DEPA and S-LMBA eliminate the load modulation of the Main, thus favoring wideband operation, but at the cost of overdriving it over the whole high-efficiency region, with unavoidable reliability and stress issues. The Main overdriving issue is also present in some of the N-stage and N-way DPAs proposed in literature [6], [7], [9], being based on output combiners that hamper the modulation of the Main load when more than one auxiliary stage is on. A viable solution for this limiting factor has been proposed in [18] and [19] and implemented at 2.65 GHz in [8]. In the latter, the novel output combiner scheme was exploited in conjunction with gate envelope tracking to mitigate the low load modulation due to the deep class-C bias of the auxiliary stages.

In general, most of the above-mentioned solutions are currently limited to single-stage hybrid demonstrators, with excellent efficiency but a limited gain (typically around 10 dB), and often complex architectures, limiting so far their adoption at higher communications frequencies, where PA architectures with one or more driver stages are inevitably called for.

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

2

Recently, 6 dB DPAs and LMBAs are starting to appear at Ka-band and 5G FR2 frequencies with competitive performance [20], [21], [22], [23], despite the need of multistage architectures. Therefore, this work aims at exploring the feasibility of deep-OBO DPAs at similar frequencies and their convenience as compared to more classical solutions with a less severe gain penalty.

Concerning these DPAs, the nomenclature is not unique; in this work, N-stage indicates N - 1 drivers and a final power stage, whereas M-way refers to a DPA with M efficiency peaks, and hence with M - 1 auxiliary devices.

In the following, a step-by-step design strategy for three-way DPAs (DPA3W) based on the combiner of [18] and [19] is provided. The complete design flow for the computation of the combiner's parameters as well as the devices' selection is presented, critically discussing the possible trade-offs and introducing general design charts to visualize the available design space when accounting for several technology constraints.

The approach is validated by the design and experimental characterization of a demonstrator targeting the FR2 5G band n261 (27.5–28.35 GHz), optimized at 6 and 12 dB OBO. The prototype, manufactured in the 150 nm GaN-SiC high-electron-mobility transistor (HEMT) process of WIN Semiconductors is, to the best of the authors' knowledge, the first monolithic microwave integrated circuit (MMIC) DPA3W. It compares well with the present state of the art at similar frequencies, demonstrating the validity of the approach and opening to the adoption of this strategy also for mm-wave applications.

This article is structured as follows. Section II reports the theoretical foundations and derives the design equations for a generic DPA3W, exploring the design space and the available degrees of freedom with the aid of graphical charts. In Section III, the theoretical formulation is applied to the design of an MMIC three-stage DPA3W demonstrator in GaN technology at 28 GHz. The experimental characterization results of the manufactured MMIC are presented in Section IV. Finally, conclusions are drawn in Section V.

## **II. THEORETICAL ANALYSIS**

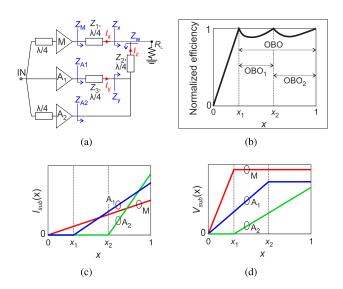

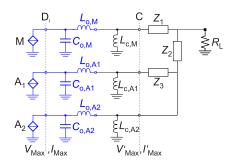

The proposed DPA3W architecture of Fig. 1(a) can synthesize the efficiency profile shown in Fig. 1(b) provided that the active devices are driven to generate current profiles like those of Fig. 1(c) and corresponding voltage response similar to those of Fig. 1(d). The two back-off efficiency peaks occur at a distance (in dB) OBO<sub>2</sub> and OBO from saturation. Assuming the simplified ideal behavior of the active devices, the following operating regions can be identified, relative to the normalized dynamic range (i.e., the driving input voltage) x (where  $0 \le x \le 1$ ).

1)  $0 \le x < x_1$  (Low Power Region): Only the Main (M) device is conducting with a fixed load condition  $Z_M$ , while the two Auxiliary devices (A<sub>1</sub> and A<sub>2</sub>) are OFF, assumed as open circuits. Hence, the impedance  $Z_w$  results in an open circuit, and the Main sees only the series of the  $\lambda/4$  transmission line (TL)  $Z_1$  and  $R_L$ .

Fig. 1. Proposed structure (a) for a DPA3W with (b) resulting efficiency, and typical profiles of (c) current and (d) voltage of the three devices.

- x<sub>1</sub> ≤ x < x<sub>2</sub> (OBO<sub>1</sub> Region): At the first break point x = x<sub>1</sub>, M achieves its maximum voltage swing (voltage saturation) and A<sub>1</sub> turns on, modulating Z<sub>M</sub>, while A<sub>2</sub> is still off. The current provided by A<sub>1</sub> increases the impedance Z<sub>x</sub>, and the λ/4 TL Z<sub>1</sub> acts as an impedance inverting network, thus decreasing the value of Z<sub>M</sub>.

- 3)  $x_2 \le x \le 1$  (*OBO*<sub>2</sub> *Region*): At the second break point  $x = x_2$ , A<sub>1</sub> reaches its maximum voltage swing (voltage saturation), and A<sub>2</sub> turns on, modulating both  $Z_{\rm M}$  and  $Z_{\rm A_1}$ . Indeed, the current injected by A<sub>2</sub> increases the impedance  $Z_{\rm y}$ , and the  $\lambda/4$  TL  $Z_3$  acts as an impedance inverting network for A<sub>1</sub>, thus decreasing the value of  $Z_{\rm A_1}$ . Simultaneously, the currents of A<sub>1</sub> and A<sub>2</sub> further increase  $Z_{\rm x}$ , thus decreasing the impedance  $Z_{\rm M}$ . At x = 1 all devices are in saturation, i.e., operate with maximum current and voltage swings.

At the input of the DPA3W, an *ad hoc* splitter is clearly required to properly compensate the phase shifts introduced by the  $\lambda/4$  TLs of the output combiner, as well as appropriately dividing the input power among the three amplifying branches, thus leading to the final architecture reported in Fig. 1(a).

The fundamental components of the drain current and voltage of each device are indicated as  $I_{sub}(x)$  and  $V_{sub}(x)$ , respectively, where sub corresponds to M, A<sub>1</sub> and A<sub>2</sub> for the Main, and the two Auxiliary devices, respectively.

The maximum voltage (peak value) for each device is

$$V_{\text{Max,sub}} = V_{\text{DD,sub}} - V_{\text{k,sub}} \tag{1}$$

where the supply  $(V_{DD,sub})$  and knee  $(V_{k,sub})$  voltages can in general be different among the stages. Therefore, it is useful to define the normalization coefficient

$$\beta_n = \frac{V_{\text{Max},A_n}}{V_{\text{Max},M}} \qquad n = 1, 2.$$

<sup>(2)</sup>

Similarly, the maximum current (peak value) of each device will be indicated in the following as  $I_{\text{Max,sub}}$ . Its relation with the fundamental current component at saturation  $[I_{\text{sub}}(1)]$

depends on the bias point of the device, i.e., its quiescent current  $I_{DQ,sub}$ . By defining the normalized quiescent current  $\xi_{sub} = I_{DQ,sub}/I_{Max,sub}$ , the relation with the peak fundamental current is

$$I_{\text{Max,sub}} = \frac{I_{\text{sub}}(1)}{I_1(\xi_{\text{sub}}, 1)}$$

(3)

where  $I_1(\xi, x)$  is the coefficient of the fundamental component of a truncated (normalized) sinusoidal waveform given by [18], [24]

$$I_{1}(\xi, x) = \frac{x}{2\pi} \cdot \frac{\theta_{x} - \sin(\theta_{x})}{1 - \cos\left(\frac{\theta_{x=1}}{2}\right)}$$

$$\theta_{x} = \begin{cases} 0, & \text{if } \xi \leq 0, \ x < \left|\frac{\xi}{1-\xi}\right| \\ 2\pi, & \text{if } \xi \geq 0, \ x < \left|\frac{\xi}{1-\xi}\right| \\ 2 \cdot \arccos\left(\frac{\xi}{x \cdot (\xi-1)}\right), \ \text{otherwise.} \end{cases}$$

$$(4)$$

Since all circuit elements are assumed to be lossless, the output power of the DPA3W is given by the sum of the output powers of the three devices

$$P_{\text{DPA}}(x) = P_{\text{M}}(x) + P_{\text{A}_{1}}(x) + P_{\text{A}_{2}}(x)$$

(6)

where

$$P_{\rm sub}(x) = \frac{1}{2} \cdot V_{\rm sub}(x) \cdot I_{\rm sub}(x). \tag{7}$$

The design relationships for the proposed DPA3W are derived by assuming as design goals the position of the efficiency peaks  $(x_1 \text{ and } x_2)$  and the target output power at saturation  $[P_{\text{DPA,sat}} = P_{\text{DPA}}(1)]$ , and as free parameters the common-node resistance  $R_{\text{L}}$  and the bias point of the Main, expressed in terms of drain voltage  $V_{\text{DD,M}}$  and quiescent current  $I_{\text{DQ,M}}$ . The characteristic impedances of the  $\lambda/4$  TLs of the output combiner  $(Z_1, Z_2, Z_3)$ , the bias points of A<sub>1</sub> and A<sub>2</sub>, and the maximum currents of all devices  $(I_{\text{Max,M}}, I_{\text{Max,A_1}}, I_{\text{Max,A_2}})$  are derived accordingly. Note that in the following the 90° phase rotation in any relation across a  $\lambda/4$  TL is omitted since all quantities represent the magnitude of the corresponding phasors. In other words, it is assumed that the phase of the branch signals is such as to ensure in-phase current summation at the common node (i.e., into  $R_{\text{L}}$ ).

## A. Derivation of the Combiner's Parameters

With reference to Fig. 1(a) and accounting for the constitutive equation of a  $\lambda/4$  TL at center frequency [25], it follows that  $I_x$  is constant for  $x_1 \le x \le 1$ . Thus, the following relevant parameters can be derived:

$$\alpha_1^2 = \frac{P_{\text{DPA}}(x_1)}{P_{\text{DPA}}(1)} = \frac{\frac{1}{2}R_{\text{L}}I_x^2(1)}{\frac{1}{2}R_{\text{L}}[I_x(1) + I_z(1)]^2} = \frac{I_x^2(1)}{[I_x(1) + I_z(1)]^2}$$

(8)

$$a_{2}^{2} = \frac{I_{\text{DPA}}(x_{2})}{P_{\text{DPA}}(1)}$$

$$= \frac{\frac{1}{2}R_{\text{L}}[I_{x}(1) + I_{z}(x_{2})]^{2}}{\frac{1}{2}R_{\text{L}}[I_{x}(1) + I_{z}(1)]^{2}} = \frac{[I_{x}(1) + I_{z}(x_{2})]^{2}}{[I_{x}(1) + I_{z}(1)]^{2}}$$

(9)

which, accounting for the generic definition of OBO =  $-10 \log_{10} P_{\text{DPA}}(x) / P_{\text{DPA}}(1)$ , are also given by

$$\alpha_1 = 10^{-(\text{OBO}/20)} \tag{10a}$$

$$\alpha_2 = 10^{-(\text{OBO}_2/20)} \tag{10b}$$

where OBO and OBO<sub>2</sub> are design goals. By combining (8) and (9), one finds a relation between the overall current coming from the Auxiliary branches  $(I_z)$  and the one of the Main  $(I_x)$ , at  $x_2$  and saturation

$$I_{z}(x_{2}) = I_{x}(x_{2}) \frac{\alpha_{2} - \alpha_{1}}{\alpha_{1}}$$

(11)

$$I_{z}(1) = I_{x}(1) \frac{1 - \alpha_{1}}{\alpha_{1}}.$$

(12)

Adopting (8) and (12),  $I_x(1)$  can be expressed as function of  $R_L$  and  $P_{DPA,sat}$

$$I_{\rm x}(1) = \alpha_1 \cdot \sqrt{\frac{2 \cdot P_{\rm DPA,sat}}{R_{\rm L}}}.$$

(13)

Since M achieves voltage saturation at  $x_1$ ,  $V_{\text{Max},M}$  is constant for  $x_1 \le x \le 1$ , which implies constant  $I_x$ . The characteristic impedance of the  $\lambda/4$  TL in front of M can be derived from (13)

$$Z_1 = \frac{V_{\text{Max,M}}}{I_x(1)} = \frac{V_{\text{Max,M}}}{\alpha_1} \cdot \sqrt{\frac{R_{\text{L}}}{2 \cdot P_{\text{DPA,sat}}}}.$$

(14)

Similarly, the characteristic impedance of the  $\lambda/4$  TL in front of A<sub>2</sub> can be derived by using (12) and (13)

$$Z_2 = \frac{V_{\text{Max,A}_2}}{I_z(1)} = \frac{\beta_2 \cdot V_{\text{Max,M}}}{1 - \alpha_1} \cdot \sqrt{\frac{R_{\text{L}}}{2 \cdot P_{\text{DPA,sat}}}}$$

(15)

whereas, considering that

$$I_{y}(x_{2}) = \frac{V_{L}(x_{2})}{Z_{2}} = \frac{R_{L} \cdot [I_{x}(x_{2}) + I_{z}(x_{2})]}{Z_{2}}$$

(16)

and by using (11), (13), and (15), the characteristic impedance of the  $\lambda/4$  TL in front of A<sub>1</sub> results

$$Z_{3} = \frac{V_{\text{Max,A}_{1}}}{I_{y}(x_{2})} = \frac{\beta_{1} \cdot \beta_{2} \cdot V_{\text{Max,M}}^{2}}{2 \cdot \alpha_{2}(1 - \alpha_{1}) \cdot P_{\text{DPA,sat}}}.$$

(17)

Notably, (14), (15), and (17) allow the synthesis of the output combiner once the values of OBO, OBO<sub>2</sub>, and  $P_{\text{DPA,sat}}$  are chosen.

## B. Derivation of the Active Devices' Parameters

To complete the synthesis of the output section of the DPA3W, it is necessary to estimate the maximum current required by each device, and thus their active periphery. This can be accomplished deriving first their fundamental component at saturation  $I_{sub}(1)$  and then the associated maximum current  $I_{Max,sub}$  by using (3)–(5). Exploiting the  $\lambda/4$  TL

IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES

properties, Kirchoff current law (KCL) at x = 1, and (14)–(6), one finds

$$I_{\rm M}(1) = \frac{V_{\rm L}(1)}{Z_1} = \frac{R_{\rm L}[I_{\rm x}(1) + I_{\rm z}(1)]}{Z_1} = \alpha_1 \frac{2P_{\rm DPA,sat}}{V_{\rm Max,M}}$$

(18)

$$I_{A1}(1) = \frac{V_{Max,A2}}{Z_3} = \frac{\alpha_2(1-\alpha_1)}{\beta_1} \cdot \frac{2P_{DPA,sat}}{V_{Max,M}}$$

(19)

$$I_{A2}(1) = 2 \frac{P_{A_2,sat}}{V_{Max,A2}} = \frac{(1 - \alpha_1 - \alpha_2 + \alpha_1 \alpha_2)}{\beta_2} \cdot \frac{2P_{DPA,sat}}{V_{Max,M}}.$$

(20)

It is worth noting that the fundamental current components do not depend on  $R_L$ , confirming that the latter can be used as a free parameter to widen the design space, i.e., increase the feasibility of the characteristic impedances of the  $\lambda/4$  TLs given by (14)–(17), in the selected technology.

Assuming the bias condition of M as a free parameter, its  $I_{\text{Max},M}$  can be derived by substituting (18) in (3) and exploiting (4) and (5)

$$I_{\text{Max},M} = \frac{I_{M}(1)}{I_{1}(\xi_{M}, 1)} = \frac{2 \cdot \alpha_{1} \cdot P_{\text{DPA},\text{sat}}}{V_{\text{Max},M} \cdot I_{1}(\xi_{M}, 1)}.$$

(21)

The maximum current of the Auxiliary devices can be derived by combining (19), (20), (18), and (3)-(5)

$$I_{\text{Max},A_1} = \frac{1}{\beta_1} \cdot I_{\text{Max},M} \cdot \frac{I_1(\xi_M, 1)}{I_1(\xi_{A_1}, 1)} \cdot \frac{\alpha_2}{\alpha_1} \cdot (1 - \alpha_1) \quad (22a)$$

$$I_{\text{Max},A_2} = \frac{\beta_1}{\beta_2} \cdot I_{\text{Max},A_1} \cdot \frac{I_1(\xi_{A_1},1)}{I_1(\xi_{A_2},1)} \cdot \left(\frac{1}{\alpha_2} - 1\right). \quad (22b)$$

To ensure the proper turn-on of the Auxiliary devices, it is possible to compute their virtual negative bias point  $\xi_{A_n}$  as

$$\xi_{A_n} = \frac{x_n}{x_n - 1}, \qquad n = 1, 2$$

(23)

being the breakpoints  $x_n$  the solutions of the following equation [24]:

$$I_1(\xi_{\rm M}, x_n) - \alpha_n \cdot I_1(\xi_{\rm M}, 1) = 0 \tag{24}$$

which defines the linear current profile of the Main device.

Finally, the impedance at the current generator plane of each device is  $Z_{d_i,\text{sub}} = V_{\text{sub}}/I_{\text{sub}}$  [which coincides with  $Z_{\text{sub}}$  in Fig. 1(a)], whereas their optimum load resistance is given by

$$R_{\rm opt,sub} = 2 \cdot V_{\rm Max,sub} / I_{\rm Max,sub}.$$

(25)

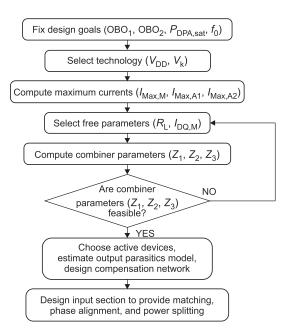

A summary of the design procedure is provided in the flowchart of Fig. 2. It is worth mentioning that the combiner topology and the corresponding system of equations reported above can be easily extended to the case of DPAs with more than two efficiency peaks, i.e., more than two Auxiliary devices.

# C. Feasibility Analysis and Design Space

The design procedure laid out up to now and summarized in Fig. 2 has no theoretical limitations and could be applied to synthesize, on paper, any M-way Doherty architecture having an arbitrary position of the efficiency peaks, saturated output power, operating frequency, etc. However, as usual, theory has

Fig. 2. Flowchart of the design procedure for a DPA3W.

to meet technology constraints to produce feasible designs. Considering MMIC technologies, once the DPA3W design goals are fixed, the main limitations associated with passive and active components are the feasibility of the characteristic impedances of the  $\lambda/4$  TLs (Z<sub>1</sub>, Z<sub>2</sub>, and Z<sub>3</sub>) and the maximum allowable current and voltage swings. Characteristic impedances can be considered feasible if included in the range 20–100  $\Omega$ , almost independently of the specific technology. The maximum current and voltage swings, instead, are heavily affected by the semiconductor proprieties of the specific technologies. This leads to the identification of the active devices macro parameters such as current density, drain bias, knee, and breakdown voltages. Focusing on GaN technology for mm-wave applications (i.e., with a gate length of the order of 0.1–0.15  $\mu$ m), the current density typically ranges within 400-1000 mA/mm, whereas recommended drain bias voltages are within 10-30 V. Both features, together with the corresponding knee voltage value, concur to determine the achievable output power from a chosen device.

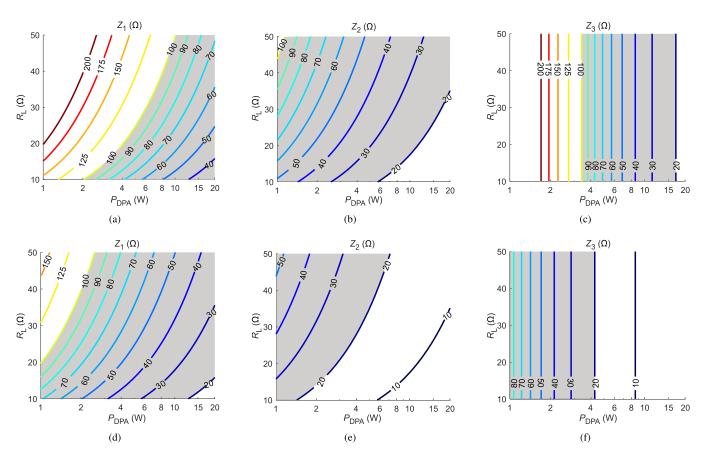

Accounting for these considerations, design charts are provided in Fig. 3 to aid the designer to visualize the contrasting constraints that influence the DPA3W design space. In particular, the contours of  $Z_i$  as functions of  $P_{\text{DPA,sat}}$  and  $R_{\text{L}}$  are reported, fixing the design goals to OBO = 12 dB and OBO<sub>2</sub> = 6 dB. Moreover, despite the developed theory allows to account for different drain bias voltage of the devices, in these charts only the cases with  $V_{\text{Max},M} = V_{\text{Max},A_1} = V_{\text{Max},A_2} = 16$  V [see Fig. 3(a)–(c)] and 8 V [see Fig. 3(d)–(f)] are reported, leaving to the readers the possibility to explore larger design spaces by accounting for different values of OBOs and  $V_{\text{Max,sub}}$ .

The available space for each parameter is highlighted in the corresponding plots with shaded areas, whose intersection represents the overall design space, considering the output power as design goal. In the first case, i.e.,  $V_{\text{Max},M,A_1,A_2} = 16$  for

Fig. 3. Design charts for the characteristic impedances  $Z_1$ ,  $Z_2$ ,  $Z_3$  of the combiner, with OBO = 12 dB and OBO<sub>2</sub> = 6 dB,  $V_{\text{Max},M} = V_{\text{Max},X_1} = V_{\text{Max},X_2} = V_{\text{Max},\text{sub}}$  (a)–(c) for  $V_{\text{Max},\text{sub}} = 16$  V and (d)–(f) for  $V_{\text{Max},\text{sub}} = 8$  V. The shaded areas correspond to the available design space, dictated by feasible characteristic impedances (20  $\Omega \leq Z_i \leq 100 \Omega$ ).

$R_{\rm L} = 50 \ \Omega$ , the resulting  $Z_1$ , would be practically unfeasible for any value of  $P_{\text{DPA,sat}} \leq 10$  W. On the contrary,  $Z_2$  is always feasible and does not pose any constraint, whereas  $Z_3$  only depends on P<sub>DPA,sat</sub> and becomes feasible for relatively high power values, above 3 W. Anyway, if a  $P_{\text{DPA,sat}} \leq 10$  W is required, the designer can select a lower value for the free parameter  $R_{\rm I}$  to accommodate such a need, at the expense of an additional post-matching network (PMN) (which inevitably impacts on area, losses, complexity). For instance, an output power of about 5 W can be achieved by setting  $R_{\rm L} = 20 \ \Omega$ which leads to more practical and feasible values of the output combiner impedances. However, Fig. 3(a)-(c) also show that  $P_{\text{DPA,sat}} \lesssim 4 \text{ W}$  is not achievable with  $V_{\text{Max},\text{M},\text{A}_1,\text{A}_2} = 16 \text{ V}$ due to the limitation on  $Z_3$ . To design a DPA3W with OBO = 12 dB and  $OBO_2 = 6 \text{ dB}$  and targeting relatively low output power, the designer has to play with the voltage swing across the devices in order to land on a feasible output combiner. For instance, Fig. 3(d)-(f) show the design charts for  $V_{\text{Max},M} = V_{\text{Max},A_1} = V_{\text{Max},A_2} = 8$  V. Notably, all the impedances become feasible and well inside the practical limits of 20–100  $\Omega$  for any  $P_{\text{DPA,sat}} \leq 4$  W, confirming both versatility and feasibility of the proposed architecture.

## III. DESIGN

In this work, the 150 nm gate length GaN-SiC HEMT process by WIN Semiconductors is adopted to design a 3 W

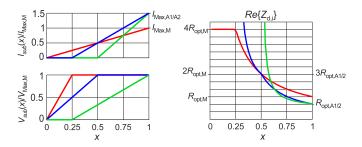

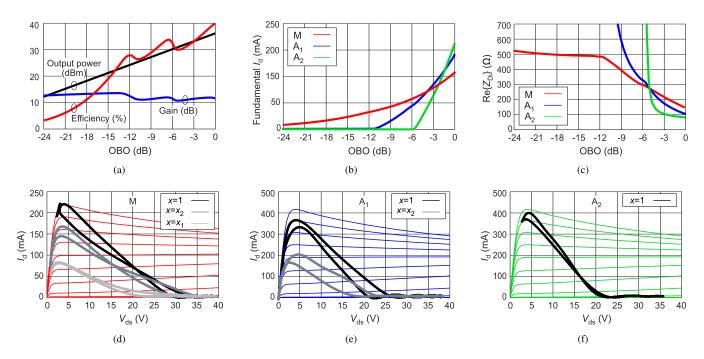

Fig. 4. Currents, voltages and impedances profiles for a 6/12 dB OBO DPA3W.

DPA3W for 5G applications around 28 GHz, optimized at 6 and 12 dB OBO. The normalized fundamental current, voltage, and impedance profiles for such an architecture assuming  $V_{\text{Max,M}} = V_{\text{Max,A1}} = V_{\text{Max,A2}} = V_{\text{Max,sub}}$  are reported in Fig. 4. Notably, the maximum current of the Auxiliary devices is 1.5 times higher than that of the Main. Therefore, either the Auxiliary devices will have a larger periphery, or the Main device will be under-utilized if three identical devices were to be used.

## A. DPA3W Assessment in the Selected Technology

The selected technology has operating voltage  $V_{DD} = 20$  V, current density around 400–500 mA/mm, and a scalable

non-linear model for the active devices. The knee voltage is estimated to be  $V_k = 4$  V, leading to  $V_{\text{Max,sub}} \leq 16$  V. Despite the developed theory allows to account for the different bias conditions of the devices, the combiner design is here carried out based on a class-B approximation for all the devices, which can be considered sufficiently accurate. Therefore, (4) reduces to  $I_1(x) = x$ , which implies  $I_{\text{Max,sub}} = 2 \cdot I_{\text{sub}}(1)$ . Following the flowchart of Fig. 2, the design charts of Fig. 3(a)–(c), and the considerations made on the technology constraints,  $R_L$  is set to =11.3  $\Omega$ , which represents a reasonable trade-off between feasibility and complexity of the combiner. The parameters computed according to (14)–(17), and the corresponding maximum currents given by (21) and (22), result

$$Z_1 = 81 \ \Omega$$

$I_{\text{Max,M}} = 110 \text{ mA}$

$Z_2 = 27 \ \Omega$   $I_{\text{Max,A1}} = 164 \text{ mA}$

$Z_3 = 97 \ \Omega$   $I_{\text{Max,A2}} = 164 \text{ mA}.$

Active devices, for which the foundry non-linear model is validated, suitable to provide the required currents are  $4 \times 75 \,\mu\text{m}$  for the Main and  $6 \times 100 \,\mu\text{m}$  for each of the Auxiliary devices. Their output parasitics model in the 27–29 GHz band is a shunt  $C_{o,sub}$ -series  $L_{o,sub}$ , as shown in Fig. 5.

A shunt  $L_{c,sub}$  compensation of the reactance is possible, but it brings about a change of the resistance, i.e., a scaling of currents and voltages, from the combiner plane (*C*) to the intrinsic drain plane (*D*<sub>i</sub>) highlighted in Fig. 5. Therefore, a recomputation of the combiner parameters is required. A more complex compensation strategy that does not modify the impedance levels is in theory possible, but it is avoided here due to the complexity and losses at this frequency. The values of the output parasitics and corresponding compensation elements are

$$C_{o,M} = 125 \text{ fF}$$

$C_{o,A1/A2} = 230 \text{ fF}$

$L_{o,M} = 36 \text{ pH}$   $L_{o,A1/A2} = 30 \text{ pH}$

$L_{c,M} = 225 \text{ pH}$   $L_{c,A1/A2} = 111 \text{ pH}.$

The voltages scale from  $V_{\text{Max,sub}} = V_{\text{DD}} - V_{\text{k}} = 16 \text{ V}$  for all devices at plane  $D_{\text{i}}$  to  $V'_{\text{Max,M}} = 13.8 \text{ V}$  and  $V'_{\text{Max,A1/A2}} = 12.6 \text{ V}$  at plane *C*, due to the different parasitic and compensation networks. Therefore, the recomputed combiner parameters and maximum currents become

$$\begin{split} & Z_1' = 70 \ \Omega \quad I_{\text{Max,M}}' = 128 \text{ mA} \\ & Z_2' = 21 \ \Omega \quad I_{\text{Max,A1}}' = 208 \text{ mA} \\ & Z_3' = 61 \ \Omega \quad I_{\text{Max,A2}}' = 208 \text{ mA}. \end{split}$$

Indeed, comparing the initial set of parameters with the final one, one can easily note that the characteristic impedances become more suitable for an MMIC implementation while the current values vary only slightly, and are still achievable with the formerly selected devices, i.e., the  $4 \times 75 \ \mu m$  for the Main and the  $6 \times 100 \ \mu m$  for each of the Auxiliary devices.

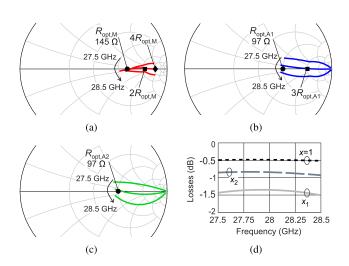

The optimum loads of the devices, computed according to (25) at plane  $D_i$ , are  $R_{opt,M} = 145 \ \Omega$  and  $R_{opt,A_1} = R_{opt,A_2} = 97 \ \Omega$ .

Fig. 5. Schematic of the DPA output combiner implemented with ideal TLs, where the transistors are represented as current sources with CL parasitics, resonated out by means of a shunt L.

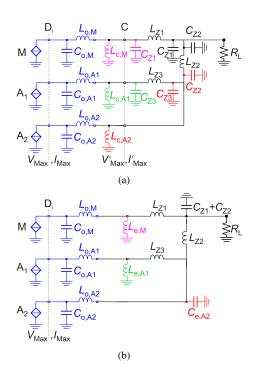

Fig. 6. Schematic of the DPA output combiner, where the transistors are represented as current sources with CL parasitics, resonated out by means of a shunt L (a) where each TL is implemented with a lumped  $\pi$  equivalent and (b) with a minimum number of elements.

#### **B.** Output Combiner Implementation

The output combiner is implemented in lumped form, replacing each  $\lambda/4$  TL section with its  $\pi$  *CLC* equivalent network derived at  $f_0 = 28$  GHz [see Fig. 6(a)]. The resulting *C* and *L*, derived according to  $C_{Zi} = 1/(2\pi f_0 Z_i)$  and  $L_{Zi} = Z_i/(2\pi f_0)$ , are given in Table I. This implementation, together with the choice of compensating the device parasitics by means of a simple shunt inductive element, allows to minimize the number of circuit components, thus also complexity and losses. In fact, as shown in Fig. 6(a) and (b), the elements connected to the same node (highlighted in the same color) are merged into one equivalent reactive element, which results inductive on the M and A1 branches ( $L_{e,M}$ ,  $L_{e,A1}$ ), and capacitive on the A2 branch ( $C_{e,A2}$ ).

The real-to-real PMN from  $R_{\rm L} = 11.3$  to 50  $\Omega$  is implemented by means of two  $\lambda/4$  TL sections, also implemented in lumped form.

TABLE I

Circuit Parameters of the Output Combiner

| $C_{Z1}$ | $L_{Z1}$ | $C_{\rm Z2}$ | $L_{Z2}$ | $C_{\rm Z3}$ | $L_{Z3}$ | $L_{e,M}$ | $L_{\rm e,A1}$ | $C_{\rm e,A2}$ |

|----------|----------|--------------|----------|--------------|----------|-----------|----------------|----------------|

| [fF]     | [pH]     | [fF]         | [pH]     | [fF]         | [pH]     | [pH]      | [pH]           | [fF]           |

| 82       | 396      | 265          | 122      | 93           | 346      | 523       | 396            | 68             |

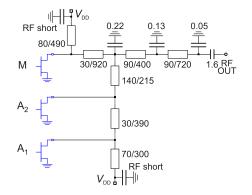

Fig. 7. Schematic of the output combiner of the DPA3W implemented in MMIC technology. Microstrip dimensions are specified as width/length (in  $\mu$ m) and capacitor values are in pF.

The resulting schematic of the DPA3W output section, translated into real circuit elements available in the selected MMIC process (where inductors are replaced by TLs due to layout as well as current handling issues) and optimized around 28 GHz, is shown in Fig. 7, where the output equivalent model of the transistors has been replaced by the full symbol (in blue). The optimization goals impose a trade-off between correct load modulation [as identified in Fig. 4 (right)] and limited losses (within -1.5 dB) across the whole dynamic range (i.e., at  $x = x_1, x_2, n1$ ). Note that, in the synthesized architecture, the position of A<sub>1</sub> and A<sub>2</sub> is swapped for layout convenience. Also, the shunt capacitor  $C_{e,A2}$  has resulted unnecessary during the optimization and has therefore been removed. The simulated load modulation and losses, adopting as device model ideal current sources with LC parasitics, are shown in Fig. 8. According to Fig. 8(a)-(c), all the devices maintain the correct load modulation, nearly on the real axis at  $f_0$ , and reasonably close to it from 27.5 to 28.5 GHz. The power losses (both mismatch and ohmic) are maintained within the targeted range across the whole high-efficiency region, and are lower at saturation than at the back-off points.

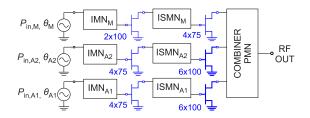

## C. Two-Stage DPA3W Architecture

Simulated power sweeps of the 4  $\times$  75  $\mu$ m and 6  $\times$  100  $\mu$ m devices at 28 GHz return power gain and peak efficiency around 10 dB and 55%, respectively, for a class-AB bias (100 mA/mm) on the optimum load.

Given the input power splitting factors required to synthesize the current profiles of Fig. 4 with the selected devices, a single-stage DPA3W architecture results unfeasible. The insertion of a driver in each of the branches is needed to ensure sufficient gain. Drivers able to correctly drive the corresponding final stage are, respectively, the  $2 \times 100 \ \mu m$ for the Main and  $4 \times 75 \ \mu m$  for the Auxiliary stages.

Fig. 8. Simulated (a)–(c) load modulation at the intrinsic drain plane  $(D_i)$  of the three power devices and (d) losses of the output section (combiner and PMN) of Fig. 7.

TABLE II CIRCUIT PARAMETERS OF THE STABILIZATION NETWORKS

| Device Periphery | $R_{\mathrm{stab},1}$ | $C_{\mathrm{stab}}$ | $R_{\mathrm{stab},2}$ | $L_{\mathrm{stab}}$ |

|------------------|-----------------------|---------------------|-----------------------|---------------------|

| $[\mu m]$        | $[\Omega]$            | [pF]                | $[\Omega]$            | [pH]                |

| 2×100            | 13                    | 2.3                 | 2.7                   | 75                  |

| 4×75             | 18                    | 3.3                 | 2.8                   | 60                  |

| 6×100            | 12                    | 3.5                 | 1.8                   | 70                  |

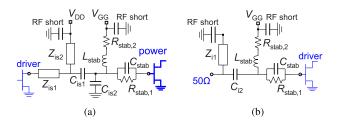

Fig. 9. Schematics of (a) ISMN and (b) IMN topologies, including the input stabilization network of the corresponding devices.

Fig. 10. Schematic of the two-stage DPA3W with three separate RF inputs.

All devices are stabilized in and out of the band by means of a series  $R_{\text{stab},1} \parallel C_{\text{stab}}$  network and a shunt  $R_{\text{stab},2}$ - $L_{\text{stab}}$  (which will be implemented as an inductive stub), whose values are reported in Table II.

The interstage (IS) and input (I) matching networks (MNs) are designed to minimize reflections, thus maximizing the power transfer along the transistor chain. The ISMNs transform the input impedance of the stabilized power devices into the optimum load of the drivers, whereas the IMNs transform

IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES

Fig. 11. Simulation results of the two-stage DPA3W with lossless IMNs and ISMNs and lossy output combiner, with three separate RF inputs optimized at 28 GHz. (a) Output power, efficiency, and gain; (b) fundamental intrinsic drain currents; and (c) intrinsic drain resistance versus OBO, and dynamic load lines of (d) M, (e) A<sub>1</sub>, and (f) A<sub>2</sub> at the intrinsic drain terminal, at  $x = x_1, x_2, 1$ .

TABLE III CIRCUIT PARAMETERS OF THE ISMNS AND IMNS

|       | ISMN      |           |               |                |               |                |          | IMN        |                        |  |

|-------|-----------|-----------|---------------|----------------|---------------|----------------|----------|------------|------------------------|--|

|       | $C_{is1}$ | $C_{is2}$ | $Z_{\rm is1}$ | $\theta_{is1}$ | $Z_{\rm is2}$ | $\theta_{is2}$ | $C_{i2}$ | $Z_{i1}$   | $\theta_{\mathrm{i}1}$ |  |

|       | [pF]      | [pF]      | $[\Omega]$    | [°]            | $[\Omega]$    | [°]            | [pF]     | $[\Omega]$ | [°]                    |  |

| М     | 0.4       | 0.4       | 66            | 71             | 42            | 48             | 0.9      | 70         | 10                     |  |

| $A_1$ | 0.5       | 0.2       | 62            | 45             | 42            | 33             | 3.7      | 65         | 10                     |  |

| $A_2$ | 0.4       | 0.3       | 53            | 57             | 40            | 39             | 3.6      | 70         | 10                     |  |

TABLE IV CIRCUIT PARAMETERS OF THE INPUT SPLITTER

| $Z_{\rm b1}$ | $Z_{\rm b2}$ | $Z_{\rm b3}$ | $Z_{\rm b4}$ | $Z_{b5}$   | $\theta_{\rm b1-5}$ | $R_{\rm iso}$ | $Z_{\rm del}$ |

|--------------|--------------|--------------|--------------|------------|---------------------|---------------|---------------|

| $[\Omega]$   | $[\Omega]$   | $[\Omega]$   | $[\Omega]$   | $[\Omega]$ | [°]                 | $[\Omega]$    | $[\Omega]$    |

| 98           | 66           | 21           | 85           | 87         | 90                  | 147           | 50            |

the input impedance of the stabilized driver devices into 50  $\Omega$ . In both cases, a similar low-order filter topology (including the required dc feed and dc block components) is adopted for all branches, in order to limit the difference in phase rotation versus frequency and to trade off between compactness and bandwidth. The ISMN and IMN topologies, shown in Fig. 9, are optimized separately for each branch, due to the different bias conditions and periphery of the devices. The values of their circuit parameters are reported in Table III.

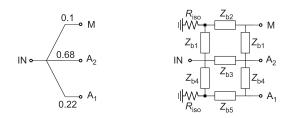

Once the combiner and MNs have been designed, the twostage DPA3W is first simulated with three independent RF inputs whose relative magnitudes and phases are optimized at  $f_0$ , as shown in Fig. 10. The non-linear models of the transistors are used, and the gate bias voltage of each is tuned to ensure the proper turn-on. Despite having in theory as many degrees of freedom as transistors, a unique gate bias voltage is used for the driver and power transistors of the same branch (i.e.,  $V_{GdM} = V_{GM}$ ,  $V_{GdA1} = V_{GA1}$ ,  $V_{GdA2} = V_{GA2}$ ), which reduces the complexity and still allows to synthesize the required current profiles. The required splitting ratios  $(P_{in,M}/P_{in} = 0.1, P_{in,A_1}/P_{in} = 0.22, P_{in,A_2}/P_{in} = 0.68)$ , and the fact that the linear gain of the Main amplifier chain is around 22 dB, allows to predict an overall gain around 12 dB for the whole two-stage DPA3W.

Fig. 11 reports the simulated performance of the two-stage DPA3W at 28 GHz, adopting the device non-linear models. The power gain is estimated assuming an ideal (lossless) input power splitting, for which  $P_{in} = P_{in,M} + P_{in,A_1} + P_{in,A_2}$ . Thanks to the optimized input driving, the obtained efficiency curve Fig. 11(a) and fundamental current profiles Fig. 11(b) are very close to those predicted by the theory. Indeed, the real part of the impedance Fig. 11(c) and the dynamic load lines Fig. 11(d)-(f) at the intrinsic drain planes of the three final devices confirm that the expected load modulation takes place. The gain of the two-stage DPA3W is around 12 dB in small signal and 10 dB at saturation, as expected, and its saturated output power is approximately 3.5 W. The efficiency peaks are around 30% at OBO, 35% at OBO<sub>2</sub>, and 40% at saturation, respectively. These are compatible with the performance estimated for the selected devices and the combiner losses estimated in Fig. 8(d), which are higher in back-off and lower at saturation.

## D. Predriver and Input Splitter

The DPA3W is completed by implementing a three-way analog splitter that feeds the branches with the required power and performs the signal alignment. Furthermore, since the gain

Fig. 12. Schematic of the three-way input splitter.

estimated for the two-stage DPA is of the order of 10 dB, a predriver stage is inserted in front of the power splitter.

Since the drivers are biased in different classes (M in class AB,  $A_1$  in shallow class C,  $A_2$  in deep class C), and it is likely that bias tuning will be required after fabrication to achieve the desired turn-on of  $A_1$  and  $A_2$ , a non-isolated power splitter is avoided due to the high sensitivity to the drivers input impedance, which may not be accurately predicted by the foundry non-linear model. An isolated power splitter provides a safer alternative, at the expense of additional losses and larger area occupation.

A three-way isolating splitter could be implemented as a cascade of two two-way power splitters, or as a single-stage 1:3 splitter. The latter is chosen to minimize area occupation. A double branchline structure, shown in Fig. 12, can synthesize the desired splitting ratios with reasonable accuracy, while providing output ports isolation of at least 10 dB. Since a 90° phase shift is present between adjacent output ports, appropriate delay lines have to be inserted on each branch. The circuit parameters are summarized in Table IV, where all the splitter TLs are 90° at  $f_0$ , the three output ports are matched to 50  $\Omega$ , and the input port impedance is 10  $\Omega$ . The latter is convenient to simultaneously keep the TLs characteristic impedances within feasible values and ease the design of the OMN of the predriver device (4  $\times$  75  $\mu$ m), which is implemented with a stub-line topology. The branchline splitter is implemented in semi-lumped form, mainly to favor layout compactness, where the low-impedance TLs are replaced by their  $\pi$  equivalent networks, as done for the combiner and PMN. Finally, the IMN of the predriver is analogous to the IMNs of the  $A_1$  and  $A_2$  drivers, since they are based on the same active device.

## IV. FABRICATION AND EXPERIMENTAL RESULTS

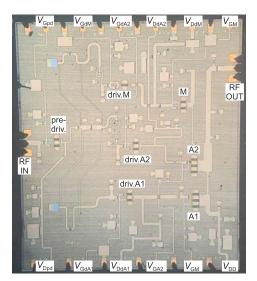

The resulting three-stage DPA3W MMIC, shown in Fig. 13, has an area of  $3.73 \times 4.2 \text{ mm}^2$ . It has been fabricated, mounted on a brass carrier with low-temperature solder paste, and dc and RF probed for the experimental characterization. The adopted dc probes are equipped with capacitors for low-frequency decoupling.

The DPA3W has been experimentally characterized in the nominal bias point  $V_{\text{DD}} = 20$  V for all devices,  $V_{\text{Gpd}} = V_{\text{GdM}} = V_{\text{GM}} = -1.8$  V,  $V_{\text{GdA1}} = V_{\text{GA1}} = -2.2$  V,  $V_{\text{GdA2}} = V_{\text{GA2}} = -2.6$  V, corresponding to an overall quiescent drain current  $I_{\text{D,tot}} = 20$  mA.

# A. Continuous Wave (CW) Measurements

The CW characterization has been performed with a precalibrated scalar setup. The input and output powers are

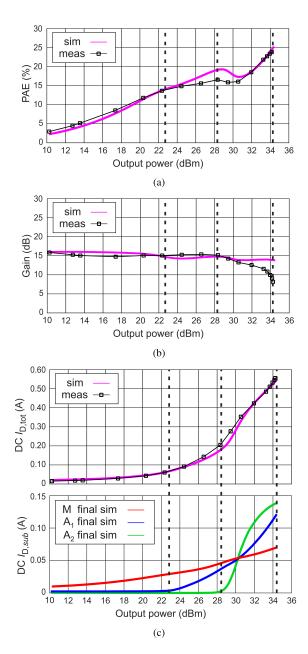

Fig. 13. Microscope photograph of the DPA3W ( $3.73 \times 4.2 \text{ mm}^2$ ).

measured in real-time with Keysight U8485A power meters. Fig. 14 reports the comparison of the CW simulated and measured performance of the DPA3W at the design frequency of 28 GHz. Fig. 14(a) PAE, Fig. 14(b) gain, and Fig. 14(c) total dc drain current (including predriver, drivers and final stages) curves plotted versus output power show a very good agreement between simulations and measurements, except for a difference of a few percentage points in terms of PAE around the turn-on point of the A<sub>2</sub> branch. To confirm the correct turn-on of  $A_1$  and  $A_2$  at 6 and 12 dB OBO, respectively, the individual dc drain current contributions of M, A<sub>1</sub>, and A<sub>2</sub> (final stages only) are also reported in Fig. 14(c). Only simulated data are available in this case, since the layout of the combiner does not allow to separate such contributions. The overall agreement of the obtained results proves the effectiveness of the presented design strategy.

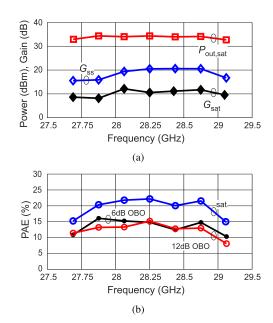

Furthermore, the DPA3W maintains a relatively flat response over a 1 GHz frequency band, from 28 to 29 GHz, as shown in Fig. 15. The saturated output power is between 34 and 34.3 dBm, with associated PAE and gain in excess of 20% and around 10 dB. The PAE is in the range 13%–16% both at 6 and 12 dB OBO.

The performance of the DPA3W is summarized and compared to the State Of the Art (SOA) in Table V. The results prove to be competitive over a 1 GHz band, especially in terms of efficiency at deep back-off, although not outperforming twoway DPAs [26], [27] in terms of efficiency at saturation and at 6 dB OBO. Furthermore, the PAE is strongly affected by the complexity in terms of presence/absence of driver stages, and thus by the gain. Single-stage DPAs [28] can achieve a remarkable efficiency even at these frequencies, but inevitably feature a very limited gain.

All in all, the theoretical advantages of a DPA3W at 5G FR2 frequencies may be hindered by the complexity of the architecture, especially to recover the inherently low gain. Therefore, future work will focus on the further simplification of the architecture and minimization of the losses.

Fig. 14. Comparison of simulated (solid) and measured (black, symbols) CW performance of the DPA3W at 28 GHz (a) PAE, (b) gain, and (c) total dc drain current (top), compared to the simulated individual contributions of the final stages (bottom). The vertical dashed lines highlight the saturation and the 12 and 6 dB OBO turn on points of the auxiliaries.

# B. Modulated Signal Measurements

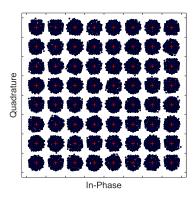

The DPA3W has then been characterized at 28 GHz under modulated signals excitation to assess its inherent linearity, i.e., without the assistance of digital predistortion. The adopted signal is a 5G NR downlink compliant 64-QAM with 40 MHz instantaneous bandwidth, compatible with the limitations of the available setup. The corresponding PAPR of the signal is 10 dB.

The adopted measurement setup includes a Keysight E8267D PSG for the signal generation and up-conversion and a Keysight N9021B MXA as receiver. The baseline

IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES

Fig. 15. Measured CW performance of the DPA3W from 27.5 to 29.25 GHz (a) saturated output power, saturated and small signal gain and (b) PAE at saturation, 6 dB OBO, and 12 dB OBO.

Fig. 16. Measured received constellation at 15 dBm average output power, with associated EVM <5% and ACPR <-32 dBc.

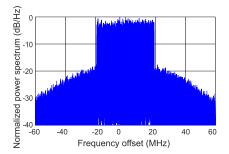

Fig. 17. Normalized output power spectrum at 25 dBm average output power, with associated PAE of 14% and ACPR <-20 dBc.

EVM and ACPR measured using an on-wafer thru are <1% and <-48 dBc, respectively.

The linearity requirements of the 3GPP for 64-QAM 5G NR signals [29] (EVM < 8% and ACPR < -28 dBc) are satisfied until an average output power of 17 dBm. At an average output power of 15 dBm, the DPA3W achieves EVM < 5% and ACPR < -32 dBc with associated PAE of 8%.

| Technology        | Frequency band<br>(GHz) | P <sub>out,sat</sub><br>(dBm) | PAE <sub>sat</sub><br>(%) | PAE <sub>6 dB obo</sub><br>(%) | PAE <sub>9 dB obo</sub><br>(%) | PAE <sub>12 dB obo</sub><br>(%) | Gain ss (sat)<br>(dB) | Ref        |

|-------------------|-------------------------|-------------------------------|---------------------------|--------------------------------|--------------------------------|---------------------------------|-----------------------|------------|

| 45 nm CMOS SOI    | 28                      | 22.4                          | 30*                       | 28                             | 20*                            | 15*                             | 10* (5*)              | [26]       |

| 28 nm CMOS        | 26                      | 18.7                          | 32*                       | 15*                            | 9*                             | 5*                              | 16* (12.5*)           | [30]       |

| 28 nm CMOS        | 27                      | 18.8                          | 30                        | 22                             | 15*                            | 10*                             | 16.5 (10*)            | [31]       |

| 28 nm CMOS        | 36                      | 22.6                          | 25*                       | 24.2                           | 12*                            | 8*                              | 18 (8*)               | [21]       |

| 150 nm GaAs       | 27.25-29.75             | 27                            | 37                        | 25                             | 15*                            | 10*                             | 18 (14*)              | [32]       |

| 90 nm GaAs        | 28                      | 30                            | 38                        | 30                             | 18*                            | 10*                             | 17.4 (10*)            | [33]       |

| 150 nm GaN-SiC    | 27–29                   | 39                            | 25                        | 21                             | 15                             | -                               | 30 (-)                | [34]       |

| 150 nm GaN-SiC    | 26-30                   | 36.1                          | 26.7                      | 25                             | 18*                            | 12*                             | 11* (7*)              | [27]       |

| 150 nm GaN-SiC    | 24–28                   | 34                            | 23                        | 14*                            | 10*                            | -                               | 18 (11)               | [35]       |

| 150 nm GaN-SiC    | 29                      | 30                            | 40                        | 28*                            | 25*                            | 20*                             | 7 (6)                 | [28]       |

| 150 nm GaN-SiC    | 28.5                    | 34.2                          | 22                        | 15                             | 14                             | 15                              | 20 (10)               | This worl  |

| 150 mill GalN-SIC | 28-29 34-3              |                               | 20-22                     | 13-16                          | 12-15                          | 13-15                           | 15-20 (8-12)          | I HIS WORK |

TABLE V Comparison Between SOA *Ka*-Band DPAs

\* Value extrapolated from graphs.

The corresponding received constellation is shown in Fig. 16. At the highest measured average output power of 25 dBm, the DPA3W achieves ACPR < -20 dBc with associated PAE of 14%. Fig. 17 shows the corresponding measured output power spectrum.

## V. CONCLUSION

This article has presented the theoretical design equations, a practical design strategy, and the implementation of a DPA3W. Based on the equations, design charts are drawn to explore the available design space. The proposed technique has been experimentally demonstrated by the design, fabrication, and characterization of a DPA3W adopting the WIN Semiconductors' 150 nm gate length GaN-SiC HEMT process. The DPA3W is optimized for 6 and 12 dB efficiency at 28 GHz, targeting 5G applications. The prototype achieves saturated output power in excess of 34 dBm and PAE of the order of 15% from 6 to 12 dB OBO, demonstrating competitive performance compared to the current SOA at similar frequencies. A very good agreement is found between simulations and measurements, thus proving the validity of the approach. A preliminary characterization with a 5G modulated signal has also been reported, demonstrating encouraging results in terms of efficiency-linearity trade-off.

#### ACKNOWLEDGMENT

The prototype presented in this article has been realized within the framework of the "mmWave Multi-Project Runs for Selected Universities" agreement between the Italian Microwave Engineering Center for Space Applications (MECSA), Rome, Italy, and WIN Semiconductors, Taoyuan City, Taiwan. The authors would like to thank Keysight, Santa Rosa, CA, USA, for providing the measurement instruments adopted for the system level characterization.

#### REFERENCES

W. H. Doherty, "A new high efficiency power amplifier for modulated waves," *Proc. IRE*, vol. 24, no. 9, pp. 1163–1182, Nov. 1936.

- [2] A. Grebennikov and S. Bulja, "High-efficiency Doherty power amplifiers: Historical aspect and modern trends," *Proc. IEEE*, vol. 100, no. 12, pp. 3190–3219, Dec. 2012.

- [3] V. Camarchia, M. Pirola, R. Quaglia, S. Jee, Y. Cho, and B. Kim, "The Doherty power amplifier: Review of recent solutions and trends," *IEEE Trans. Microw. Theory Techn.*, vol. 63, no. 2, pp. 559–571, Feb. 2015.

- [4] R. Figueiredo, N. B. Carvalho, A. Piacibello, and V. Camarchia, "Nonlinear dynamic RF system characterization: Envelope intermodulation distortion profiles—A noise power ratio-based approach," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 9, pp. 4256–4271, Sep. 2021.

- [5] O. Hammi, S. Carichner, B. Vassilakis, and F. M. Ghannouchi, "Effects of crest factor reduction on the predistortion performance for multicarrier 3G RF power amplifiers," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2009, pp. 1085–1088.

- [6] N. Srirattana, A. Raghavan, D. Heo, P. E. Allen, and J. Laskar, "Analysis and design of a high-efficiency multistage Doherty power amplifier for wireless communications," *IEEE Trans. Microw. Theory Techn.*, vol. 53, no. 3, pp. 852–860, Mar. 2005.

- [7] W. C. E. Neo, J. Qureshi, M. J. Pelk, J. R. Gajadharsing, and L. C. N. de Vreede, "A mixed-signal approach towards linear and efficient *N*-way Doherty amplifiers," *IEEE Trans. Microw. Theory Techn.*, vol. 55, no. 5, pp. 866–879, May 2007.

- [8] I. Kim, J. Moon, S. Jee, and B. Kim, "Optimized design of a highly efficient three-stage Doherty PA using gate adaptation," *IEEE Trans. Microw. Theory Techn.*, vol. 58, no. 10, pp. 2562–2574, Oct. 2010.

- [9] A. Barthwal, K. Rawat, and S. K. Koul, "A design strategy for bandwidth enhancement in three-stage Doherty power amplifier with extended dynamic range," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 2, pp. 1024–1033, Feb. 2018.

- [10] R. Alsulami et al., "A novel 3-way dual-band Doherty power amplifier for enhanced concurrent operation," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 9, pp. 4041–4058, Sep. 2021.

- [11] H. Zhou, J.-R. Perez-Cisneros, S. Hesami, K. Buisman, and C. Fager, "A generic theory for design of efficient three-stage Doherty power amplifiers," *IEEE Trans. Microw. Theory Techn.*, vol. 70, no. 2, pp. 1242–1253, Feb. 2022.

- [12] P. Saad, R. Hou, R. Hellberg, and B. Berglund, "A 1.8–3.8-GHz power amplifier With 40% efficiency at 8-dB power back-off," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 11, pp. 4870–4882, Nov. 2018.

- [13] G. Lv, W. Chen, X. Chen, F. M. Ghannouchi, and Z. Feng, "A fully integrated 47.6% fractional bandwidth GaN MMIC distributed efficient power amplifier with modified input matching and power splitting network," *IEEE Trans. Microw. Theory Techn.*, vol. 69, no. 6, pp. 3132–3145, Jun. 2021.

- [14] R. Quaglia and S. Cripps, "A load modulated balanced amplifier for telecom applications," *IEEE Trans. Microw. Theory Techn.*, vol. 66, no. 3, pp. 1328–1338, Mar. 2018.

12

- [15] Y. Cao and K. Chen, "Pseudo-Doherty load-modulated balanced amplifier with wide bandwidth and extended power back-off range," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 7, pp. 3172–3183, Jul. 2020.

- [16] J. Pang, C. Chu, Y. Li, and A. Zhu, "Broadband RF-input continuousmode load-modulated balanced power amplifier with input phase adjustment," *IEEE Trans. Microw. Theory Techn.*, vol. 68, no. 10, pp. 4466–4478, Oct. 2020.

- [17] P. Saad and R. Hou, "Symmetrical load modulated balanced power amplifier with asymmetrical output coupling for load modulation continuum," *IEEE Trans. Microw. Theory Techn.*, vol. 70, no. 4, pp. 2315–2327, Apr. 2022.

- [18] P. Colantonio, F. Giannini, and E. Limiti, *High Efficiency RF and Microwave Solid State Power Amplifiers*. Hoboken, NJ, USA: Wiley, 2009, doi: 10.1002/9780470746547.ch11.

- [19] J. Gajadharsing, "Recent advances in Doherty amplifiers for wireless infrastructure," presented at the IEEE MTT-S Int. Microw. Symp. Dig., Jun. 2009.

- [20] C. Ramella, V. Camarchia, A. Piacibello, M. Pirola, and R. Quaglia, "Watt-level 21–25-GHz integrated Doherty power amplifier in GaAs technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 31, no. 5, pp. 505–508, May 2021.

- [21] V. Qunaj and P. Reynaert, "A Ka-band Doherty-like LMBA for high-speed wireless communication in 28-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 56, no. 12, pp. 3694–3703, Dec. 2021.

- [22] A. Piacibello et al., "A 5-W GaN Doherty amplifier for Kaband satellite downlink with 4-GHz bandwidth and 17-dB NPR," *IEEE Microw. Wireless Compon. Lett.*, vol. 32, no. 8, pp. 964–967, Aug. 2022.

- [23] R. Giofre, A. D. Gaudio, and E. Limiti, "A 28 GHz MMIC Doherty power amplifier in GaN on Si technology for 5G applications," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2019, pp. 611–613.

- [24] P. Colantonio, F. Giannini, R. Giofrè, and L. Piazzon, "The AB-C Doherty power amplifier—Part I: Theory," *Int. J. RF Microw. Comput.-Aided Eng.*, vol. 19, no. 3, pp. 293–306, May 2009.

- [25] P. Colantonio, F. Giannini, R. Giofrè, and L. Piazzon, "The AB-C Doherty power amplifier—Part II: Validation," *Int. J. RF Microw. Comput.-Aided Eng.*, vol. 19, no. 3, pp. 307–316, May 2009, doi: 10.1002/mmce.20351.

- [26] N. Rostomyan, M. Özen, and P. Asbeck, "28 GHz Doherty power amplifier in CMOS SOI with 28% back-Off PAE," *IEEE Microw. Compon. Lett.*, vol. 28, no. 5, pp. 446–448, May 2018.

- [27] Y. Yamaguchi, K. Nakatani, and S. Shinjo, "A wideband and high efficiency Ka-band GaN Doherty power amplifier for 5G communications," in *Proc. IEEE BiCMOS Compound Semiconductor Integr. Circuits Technol. Symp. (BCICTS)*, Nov. 2020, pp. 1–4.

- [28] R. Ishikawa, T. Seshimo, Y. Takayama, and K. Honjo, "A 28-GHz-band GaN HEMT MMIC Doherty power amplifier designed by load resistance division adjustment," in *Proc. 16th Eur. Microw. Integr. Circuits Conf.* (*EuMIC*), Apr. 2022, pp. 241–244.

- [29] Generation Partnership Project; Technical Specification Group Radio Access Network; NR; Base Station (BS) Radio Transmission and Reception (Release 15), Standard TS 38.104, v.15.5.0, 3rd Generation Partnership Project-3GPP, Section 9, Mar. 2019.

- [30] G. Cho and S. Hong, "Ka-band CMOS power amplifier based on transmission line transformers with single-ended Doherty network," *IEEE Microw. Wireless Compon. Lett.*, vol. 31, no. 11, pp. 1223–1226, Nov. 2021.

- [31] S. Kim, H.-C. Park, D. Kang, D. Minn, and S.-G. Yang, "A 24.5–29.5GHz broadband parallel-to-series combined compact Doherty power amplifier in 28-nm bulk CMOS for 5G applications," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, Jun. 2021, pp. 171–174.

- [32] A. Degirmenci and A. Aktug, "A high gain Ka-band asymmetrical GaAs Doherty power amplifier MMIC for 5G applications," in *Proc. 14th Eur. Microw. Integr. Circuits Conf. (EuMIC)*, Sep. 2019, pp. 116–119.

- [33] H. Xie, Y. J. Cheng, and Y. Fan, "A Ka-band watt-level high-efficiency integrated Doherty power amplifier in GaAs technology," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Nov. 2021, pp. 287–289.

- [34] D. Wohlert, B. Peterson, T. R. M. Kywe, L. Ledezma, and J. Gengler, "8-watt linear three-stage GaN Doherty power amplifier for 28 GHz 5G applications," in *Proc. IEEE BiCMOS Compound semiconductor Integr. Circuits Technol. Symp. (BCICTS)*, Nov. 2019, pp. 1–4.

- [35] M. Bao, D. Gustafsson, R. Hou, Z. Ouarch, C. Chang, and K. Andersson, "A 24–28-GHz Doherty power amplifier with 4-W output power and 32% PAE at 6-dB OPBO in 150-nm GaN technology," *IEEE Microw. Wireless Compon. Lett.*, vol. 31, no. 6, pp. 752–755, Jun. 2021.

Anna Piacibello (Member, IEEE) was born in Chivasso, Italy, in 1991. She received the bachelor's and master's degrees in electronic engineering and the Ph.D. degree (cum laude) in electric, electronic and communication engineering from the Politecnico di Torino, Turin, Italy, in 2013, 2015, and 2019, respectively.

In 2017, she was a Visiting Researcher with the Centre for High Frequency Engineering (CHFE), Cardiff University, Cardiff, U.K. She is currently an Assistant Professor with the Department of Elec-

tronics and Telecommunications, Politecnico di Torino. Her research interests include the design and characterization of microwave and millimeter-wave electronic circuits, mainly focusing on broadband highly efficient power amplifiers.

Dr. Piacibello has been an Affiliate Member of the IEEE MTT-S Technical Committee TC-12 on Microwave High-Power Techniques since 2022. She was a recipient of the 2018 Young Engineer Prize awarded by the European Microwave Association (EuMA).

Vittorio Camarchia (Senior Member, IEEE) was born in Turin, Italy, in 1972. He received the Laurea and Ph.D. degrees in electronic engineering from the Politecnico di Torino, Turin, in 2000 and 2003, respectively.

He was a Visiting Researcher with the Department of Electrical and Computer Engineering, Boston University, Boston, MA, USA. In 2004, he joined the Department of Electronics and Telecommunications, Politecnico di Torino, where he is currently an Associate Professor. His research has been supported

by the European Space Agency (ESA). He is also an External Reviewer for space related calls for the Research Executive Agency of the European Commission. He has published 160 peer-reviewed articles, two books, and several book chapters. His research interests are focused on modeling, design and characterization of RF and microwave modules and systems.

Prof. Camarchia is member of the IEEE MTT-S IEEE MTT-S Technical Committees TC-12 on Microwave High-Power Techniques and TC-23 on Wireless Communications and serves as a member of the International Microwave Symposium (IMS) Technical Program Review Committee on power amplifiers. He was a recipient of the 2002 Young Graduated Research Fellowship presented by the Gallium Arsenide Application Symposium Association (GAAS) Association. He has organized several workshops and focus sessions at European Microwave Week (EuMW) and IMS on nonlinear measurements, microwave backhaul, 5G and mm-wave applications, and mm-wave power amplifier design. He has served as an Associate Editor for the IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES and a Guest Editor for the Special Issue on Broadband Millimeter-Wave Power Amplifiers in 2020.

**Paolo Colantonio** (Senior Member, IEEE) received the Laurea degree in electronics engineering and the Ph.D. degree in microelectronics and telecommunications from the University of Rome Tor Vergata, Rome, Italy, in 1994 and 2000, respectively.

He is currently a Full Professor of microwave electronics with the University of Rome Tor Vergata. He is the author or a coauthor of more than 300 scientific articles. He has authored the book *High Efficiency RF and Microwave Solid State Power Amplifiers* (Wiley, 2009), three book chapters, four

contributions to *Encyclopedia of RF and Microwave Engineering* (Wiley), and one international patent. His research activities are mainly focused on the field of microwave and millimeter-wave electronic, and in particular on the design criteria for non-linear microwaves subsystems and high-efficiency power amplifiers.

Dr. Colantonio has been the Chair of European Microwave Integrated Circuits Conference (EuMIC) 2022. He is currently an Associate Editor of IEEE MICROWAVE AND WIRELESS COMPONENTS LETTERS.

**Rocco Giofrè** (Senior Member, IEEE) received the Ph.D. degree in electronics from the University of Rome Tor Vergata, Rome, Italy, in 2008.

He joined the Department of Electronics Engineering, University of Rome Tor Vergata, in 2009, where he is currently an Associate Professor of electronics. His research activities belong to the microwave and millimeter-wave electronics area ranging from active devices characterization to the design and test of linear and nonlinear circuits and systems. In this wide research area, he is mainly focused on the

development of innovative power amplifiers' schemes and architectures with high efficiency and linearity for both ground and space communication systems, including their integration in multifunctional chips such as single-chip front ends. He is involved in many research projects funded by international research agencies, such as the European Space Agency (ESA) and the Research Executive Agency (REA) of the European Commission. He has published more than 190 peer-reviewed articles, two book chapters, and two contributions for the *Encyclopedia of Electrical and Electronics Engineering* (Wiley).

Prof. Giofrè is a member of the IEEE MTT-S Technical Committee TC-12 on Microwave High-Power Techniques. He was a recipient of the 2005 Young Graduated Research Fellowship presented by the Gallium Arsenide Application Symposium Association (GAAS) Association and the Best Paper Award at the European Microwave Integrated Circuits Conference (EuMIC) 2007. He is also an Associate Editor of IEEE ACCESS journal and a reviewer of the major journals and conferences of the field.

Open Access funding provided by 'Politecnico di Torino' within the CRUI CARE Agreement