# Gate-Source Distance Scaling Effects in H-Terminated Diamond MESFETs

Claudio Verona, Walter Ciccognani, Sergio Colangeli, Fabio Di Pietrantonio, Ennio Giovine, Ernesto Limiti, Marco Marinelli, and Gianluca Verona-Rinati

Abstract—In this paper, an analysis of gate-source and gate-drain scaling effects in MESFETs fabricated on hydrogenterminated single-crystal diamond films is reported. The experimental results show that a decrease in gate-source spacing can improve the device performance by increasing the device output current density and its transconductance. On the contrary, the gate-drain distance produces less pronounced effects on device performance. Breakdown voltage, knee voltage, and threshold voltage variations due to changes in gate-source and drain-source distances have also been investigated. The obtained results can be used as a design guideline for the layout optimization of H-terminated diamond-based MESFETs.

*Index Terms*—Diamond, MESFETs, output current, semiconductor device manufacture, transconductance.

### I. Introduction

DIAMOND is a semiconductor material featured by outstanding physical, mechanical, and chemical properties if compared with other semiconductors widely adopted in electronic device fabrication, e.g., Si, GaAs, 4H-SiC, and GaN. Wide-bandgap (5.5 eV), high breakdown electric field (10000 kV/cm), low dielectric constant (5.7), high thermal conductivity (22 W/cm · K), and high electron saturation velocity (2.7 · 10<sup>7</sup> cm/s) are the examples of its distinctive physical properties [1], [2]. Diamond is thus expected to be suitable for the fabrication of high-power and high-frequency electronic devices for applications in many different fields, such as in communication satellites and radars. This has pushed research groups worldwide to realize electronic devices on single- and poly-crystalline diamond films aimed at demonstrating such suitability [3]–[5]. The p-type conductive characteristics of hydrogen-terminated

Manuscript received September 9, 2014; revised December 12, 2014 and January 14, 2015; accepted January 30, 2015. Date of publication February 17, 2015; date of current version March 20, 2015. The review of this paper was arranged by Editor S. Bandyopadhyay.

C. Verona, M. Marinelli, and G. Verona-Rinati are with the Dipartimento di Ingegneria Industriale, Università di Roma Tor Vergata, Rome 00133, Italy (e-mail: claudio.verona@uniroma2.it; marco.marinelli@uniroma2.it; gianluca.verona.rinati@uniroma2.it).

W. Ciccognani, S. Colangeli, and E. Limiti are with the Dipartimento di Ingegneria Elettronica, Università di Roma Tor Vergata, Rome 00133, Italy (e-mail: walter.ciccognani@uniroma2.it; sergio.colangeli@uniroma2.it; limiti@ing.uniroma2.it).

F. Di Pietrantonio is with the National Research Council—Istituto di Acustica e Sensoristica O.M. Corbino, Rome I-00133, Italy (e-mail: fabio.dipietrantonio@idasc.cnr.it).

E. Giovine is with the National Research Council—Istituto di Fotonica e Nanotecnologie, Rome 00156, Italy (e-mail: giovine@ifn.cnr.it).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2015.2398891

diamond surface were reported in [6] and its application to a FET device was first demonstrated in [7]. A hole accumulation in the subsurface region is originated by the energy band bending due to the interaction of hydrogen-terminated diamond surface with adsorbed ions also present in the atmosphere. In this way, the 2-D hole gas (2-DHG) is formed only below the H-terminated surface and is used as an active channel in FET devices.

Diamond MESFET realization relies on a few technological steps. In particular, device performance is mainly dependent on crystal quality of grown diamond films and its surface termination, metal/diamond junction characteristics, and geometrical factors. In this respect, a large number of diamond MES-FET structures and various optimizations have been reported in [8]-[10]. Among them, the influence of the crystalline and surface properties of the homoepitaxial diamond layer has been analyzed in [11]. The effects of device passivation (e.g., with Al<sub>2</sub>O<sub>3</sub>, AlN, and MO<sub>3</sub>) have been also studied [12]-[18] to overcome the thermal instabilities and drifts from which the surface channel of diamond MESFETs suffers. In addition, enhancement and stabilization of hole concentration in hydrogen-terminated diamond surface have been reported using different gas species (e.g., O<sub>3</sub>, NO<sub>2</sub>, and NO) and MO<sub>3</sub> deposition [16]–[19]. Finally, the scaling effect of gate length on the RF and dc performance of hydrogen-terminated diamond FETs have been studied [9], [20], [21].

The peculiar transport characteristic of diamond still offers the possibility to enhance the device performance by proper geometry optimization. For instance, Russo and Di Carlo [22] reported the simulation results on the effects of scaling gate-source ( $L_{GS}$ ) and gate-drain ( $L_{GD}$ ) distances, as well as gate length  $(L_G)$ , in GaN-based HEMTs, whereas Deng et al. [23] carried out a similar theoretical study on SiC MESFETs. In the references above, the current density increase in the active channel associated to a reduction of the gate-source distance is shown to be due to the peculiar velocity-field characteristics of GaN or SiC semiconductors, in which the ohmic (linear) regime extends up to electric fields in the order of 100 kV/cm [23], [24]. Such a physical property can be transposed to diamond devices, characterized by saturation electric fields [25] close to the values reported for GaN and SiC. To the best of the authors' knowledge, such study has not been performed yet on H-terminated diamond MESFETs.

The aim of this paper is to investigate, through an extensive measurement campaign, the dc performance of H-terminated diamond devices as a function of geometric parameters  $L_{\rm GS}$  and  $L_{\rm GD}$ . A description of the adopted single-crystal diamond growth procedure is given first. The diamond MESFET fabrication process is then briefly addressed, describing the realized device geometries. Finally, a description of the adopted test bench and the measurements performed on the samples with different geometries are presented, and the results are discussed.

### II. CVD SINGLE-CRYSTAL DIAMOND GROWTH

A high-quality single-crystal diamond film with a thickness of about 2  $\mu$ m was homoepitaxially grown by microwave plasma-enhanced chemical vapor deposition (CVD) on a 4.5  $\times$  4.5  $\times$  0.5 mm³ commercial low-cost synthetic high-pressure high-temperature 1b-type diamond (1 0 0) substrate polished on one side. No dopants were intentionally added during the deposition process. Nevertheless, the presence of an acceptor concentration of the order of  $10^{14}$  cm $^{-3}$  has been observed in [26] using diamond samples grown in the very same deposition conditions.

Prior to fabricating the devices, the diamond surface has been terminated with hydrogen (H-termination) to form a p-type channel. H-surface termination was performed by exposing the diamond surface to H plasma *in situ*, i.e., in the same microwave CVD reactor, at the end of the growth. In particular, the following two-step procedure was adopted: 1) the deposited diamond film was exposed to a hydrogen plasma for 20 min and 2) after the microwave power switch-OFF, the sample was cooled down to room temperature in a pure hydrogen atmosphere.

The surface morphology study was performed by an atomic force microscope in contact mode with the CVD diamond sample. A homogeneous surface with an average roughness of about 5-nm rms over  $10-\mu m$  area was observed. It is worth pointing out that the diamond surface was free of defects such as pyramidal hillocks, flat hillocks, and unepitaxial crystallites.

Four Au ohmic contacts were then evaporated in the van der Pauw configuration for Hall measurements at room temperature in air. A surface carrier density and a hole mobility of about  $1.1 \cdot 10^{13}$  cm<sup>-2</sup> and 110 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> were measured, respectively. In addition, the electrical properties of Au/H-terminated diamond contacts were investigated by current–voltage (I–V) measurements at room temperature in air. A sheet resistance of about 6.5 k $\Omega$ /sq and an ohmic contact resistance of 4  $\Omega$  · mm were obtained by the transmission line method.

# III. MESFET Device Fabrication Process and Device Characterization

The devices were realized on the CVD diamond homoepitaxial layer by exploiting the following fabrication process.

A 200-nm Au film was thermally evaporated on the H-terminated diamond surface and used for source and drain ohmic contacts. A polymethyl methacrylate resist,

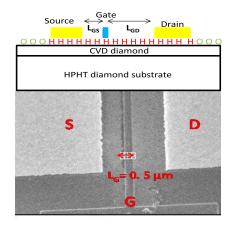

Fig. 1. Top: sketch of the device structure. Bottom: SEM picture of a typical channel geometry.

covering the device area, was patterned by a first electron-beam lithography (EBL) step and used as mask for wet etching of gold by KI/I<sub>2</sub>. To electrically insulate the devices on the same diamond substrate, the diamond surface exposed was oxidized by reactive ion etching (RIE) in a low-energy Ar and O<sub>2</sub> plasma gas mixture. The isolation was established to force the drain-source current to flow underneath the gate, thereby avoiding parasitic resistive effects. The RIE treatment used to electrically isolate the devices exhibits a diamond surface etching depth of about 1.5 nm.

To realize the drain-source channel of the MESFETs, a second EBL step was performed, followed by the Au wet chemical etching that gives rise to the separation between the source and drain contacts.

Finally, an aluminum Schottky contact (150-nm thick) was used as gate electrode. To place the gate in the channel at different distances from source and drain contacts, a third EBL step was used. The gate fabrication process finished with electron gun evaporation of aluminum and lift-off technique.

A sketch of a diamond MESFET device cross section and a scanning electron microscope (SEM) image of the device active area are shown in Fig. 1.

Many devices were fabricated on the same substrate, each of which is featured by a single gate finger with 0.5- $\mu$ m width ( $L_G$ ) and 50- $\mu$ m length (W), whereas  $L_{GS}$  and  $L_{GD}$  vary as detailed in the following. To maximize the number of devices per geometry on the substrate, a compact simplified layout, accessible via three dc pads, has been devised. The devices can then be easily tested by choosing, according to the need, which pad is to be used as the source/drain. As a consequence, the range of available  $L_{GS}$ ,  $L_{GD}$  pairs is expanded by simply inverting the supply scheme applied to a relatively small set of fixed geometries.

Realized devices can be grouped in two sets: in the first one, the total drain-source length was kept fixed ( $L_{\rm DS}=L_{\rm GS}+L_G+L_{\rm GD}=6.5~\mu{\rm m}$ ) while varying the gate finger position; in the second set, the gate-source (gate-drain) distance was varied in the range 1.0-2.6  $\mu{\rm m}$  while keeping the gate-drain (gate-source) distance fixed to

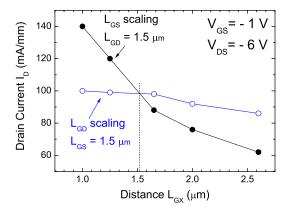

Fig. 2. Drain current density as a function of  $L_{\rm GS}$  and  $L_{\rm GD}$  distances. Gate width is 50  $\mu$ m. Gate length is 0.5  $\mu$ m.

about 1.5  $\mu$ m (therefore, changing also the total drain–source length).

All devices have been characterized under different bias conditions to identify some key parameters or to test the devices till the occurrence of the device breakdown. Measurements have been performed using a Cascade Microtech RF-1 probe station, jointly with three dc micropositioners to properly handle and contact the devices under test. DC measurements have been performed with a proprietary LabVIEW software in conjunction with a Hewlett Packard power supply (6622A) and four Hewlett Packard multimeters (34401A), two configured as voltmeters and the remaining as ampmeters. Breakdown tests have been performed with a Keithley (model 6517B) electrometer.

## IV. RESULTS AND DISCUSSION

Drain current density as a function of  $L_{\rm GS}$  and  $L_{\rm GD}$  and measured in a fixed bias condition, namely,  $V_{\rm GS} = -1$  V and  $V_{\rm DS} = -6$  V, is shown in Fig. 2. Scaling  $L_{\rm GD}$  has nearly no effect on the current density, in contrast with the  $L_{\rm GS}$  scaling, which has a noticeable impact on drain output current density. In particular, the latter increases by a factor of about 2.3 when the  $L_{\rm GS}$  distance is shortened from 2.6 to 1.0  $\mu$ m.

This behavior has already been theoretically predicted in other wide-bandgap semiconductor technologies, such as GaN-HEMT [22] and 4H-SiC MESFETs [23]. Russo and Di Carlo [22] and Deng et al. [23] supported from 2-D device simulations discuss the gate-source distance scaling effect by considering the peculiar velocity-field characteristics of GaN and 4H-SiC materials. The key feature, as already mentioned, is the ohmic regime extending up to about 100 kV/cm [23], [24]. More in detail, the downscaling of  $L_{GS}$  enhances the electric-field component along the channel between source and gate  $(E_{GS})$  and, proportionally, the average carrier velocity in the same region. Assuming the carrier density between source and gate is approximately constant (also with respect to  $L_{GS}$ ), the effect is an increased current density, which flows all the way to the drain. However, in the gate-drain region, much higher applied fields (at least one order of magnitude higher) take place in normal operation so that carrier velocity reaches the

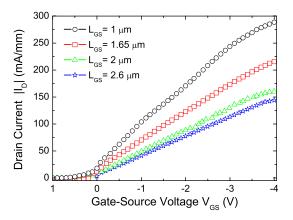

Fig. 3. Drain current density as a function of  $V_{\rm GS}$ , with  $L_{\rm GS}$  as a parameter, for  $V_{\rm DS}=-6$  V.

saturation value. In conjunction with this phenomenon, charge conservation imposes an increase in the carrier density, which indeed is maximum under the gate metallization, as verified in [22] and [23]. As a result, the  $E_{GS}$  increase produced by downscaling  $L_{GS}$  boosts the current density in saturation. Conversely, the downscaling of  $L_{GD}$  does not produce any increase in the electric field in the source-gate region, thus not affecting the saturated drain current. On the basis of [25], a similar behavior should be expected for H-terminated diamond devices. In [25], in more detail, the threshold fields for the onset of the nonlinear carrier velocity regime are shown, both for bulk and surface holes. Threshold values in the range 10-100 kV/cm have been reported, where the lower bound is associated with bulk holes and a low level of impurities per volume, whereas the upper bound is associated with bulk holes and a high level of impurities per volume or, equivalently, with superficial holes in the 2-DHG.

The drain current density measured for a fixed drain–source voltage ( $V_{\rm DS} = -6 \text{ V}$ ) as a function of the applied gate–source voltage is reported in Fig. 3 for different  $L_{\rm GS}$ , whose value is ranging from 1.0 to 2.6  $\mu$ m.

The drain current ( $I_D$ ) measured in Fig. 3 is about 20% less than that reported in Fig. 2 at the same bias point. Repeated measurements of dc drain I-V ( $I_D-V_{DS}$ ) characteristics show that drain current decreases appreciably due to channel degradation. This phenomenon has already been reported in [4] and [21] for diamond-based MESFETs.

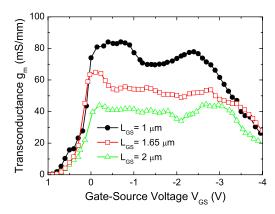

It can be observed that  $L_{\rm GS}$  scaling only affects the slope of the transcharacteristics. The threshold voltage is only slightly influenced and is estimated to be about +0.3 V in all cases. At  $V_{\rm GS}=-4$  V, the transcharacteristics start bending down, implying that the maximum attainable current density is probably only slightly higher than the one achieved at -4 V. This is consistent with the rapid decrease in the dc transconductance,  $g_m$ , shown in Fig. 4 for  $V_{\rm GS}$  values lower than 2.5 V. In Fig. 4, the positive impact on the transconductance values when downscaling  $L_{\rm GS}$  is also evident: a decrease in  $L_{\rm GS}$  from 2 to 1  $\mu$ m results in an increase in  $g_m$  from 40 to 85 mS/mm.

The double-hump shape clearly shown in Fig. 4 by the transconductance associated to the smallest  $L_{GS}$  has already

Fig. 4. DC transconductance per unit gate width as a function of  $V_{\rm GS}$ , with  $L_{\rm GS}$  as a parameter, for  $V_{\rm DS}=-6$  V.

been observed in [27]–[29] and may evoke the behavior of a double-channel device [30], [31]. It is therefore worth noting that in the present case of H-terminated diamond FETs, a single 2-DHG was sought, and no intentional measures were taken to produce an additional channel. As a consequence, it is not possible to establish with sufficient confidence what effect originates the observed double hump: this topic may deserve further investigation on the basis of advanced physical simulations. At any rate, physical models presented so far in [25], [32], and [33] are not suited to predict the observed transconductance humps.

It is worth to mention that gate current leakage, constantly monitored during the whole measurement campaign, never exceeded values as low as 7  $\mu$ A/mm (worst case taken at  $V_{\rm GS}=-3.2$  V and  $V_{\rm DS}=-15$  V). Furthermore, no evident dependences of gate leakage on gate–source or gate–drain distances were observed.

Although this paper is aimed at understanding the dc properties of H-terminated diamond devices as the gate-source distance is scaled down, some remarks about the cutoff frequency  $(f_T)$  and the maximum oscillation frequency  $(f_{\text{max}})$  as functions of scaling can be done as well. In particular, the equation correlating transconductance to the intrinsic FET cutoff frequency,  $f_T = g_m/2\pi C_{gs}$ , may let the reader infer that  $f_T$  increases proportionally to  $g_m$ . However, the increase in the electron density under the gate actually reduces the size of the pinchoff region at the drain end of the gate. This results in an increase in the gate capacitance  $(C_{gs})$ so that the  $g_m/C_{gs}$  ratio stays nearly constant. Such a conduction mechanism in the channel is very similar to what observed in GaN and 4H-SiC devices, with the only exception that holes rather than electrons are the carriers involved in the case of H-terminated diamond-based FETs. Indeed, in all of the above-mentioned devices, a 2-D free-carrier gas under the gate is present (2DEG for GaN and 4H-SiC and 2-DHG for diamond), while the region between the gate and source is almost in ohmic regime (for the applied voltages and considered geometries): an analogous behavior is therefore expected. In contrast, the maximum oscillation frequency could positively benefit from gate-source scaling, as pointed out in [23]. However, this could not be verified on the

Fig. 5. Drain current density as a function of  $V_{\rm DS}$ , for  $V_{\rm GS}=0$  V, for breakdown voltage evaluation.

available diamond devices, since they were not explicitly designed to be RF tested, as noted in Section III.

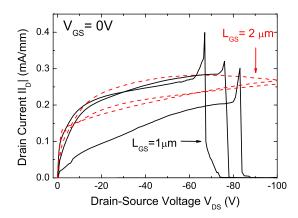

To evaluate the effect of scaling on the maximum attainable output power densities, a thorough investigation on breakdown voltage was performed as well. It is expected that a shorter  $L_{\rm GS}$  corresponds to higher carrier densities under the gate metal and to higher peaks of the horizontal electric field under the drain side of the gate. As the field reaches values high enough to establish avalanche multiplication in the device, the carrier concentration determines how steeply the current will grow up to the eventual burnout of the device.

Obviously, the higher the carrier concentration, the sooner breakdown will occur. This is confirmed by the experimental results reported in Fig. 5, where the drain current of several devices is plotted against the drain–source voltage,  $V_{\rm GS}$ , while keeping  $V_{\rm GS}$  at 0 V.

The experimental results for devices with  $L_{\rm GS} \sim 1~\mu{\rm m}$  allow estimating a breakdown voltage of about 80 V, although a noticeable spread in the order of  $\pm 10~{\rm V}$  is observed. Such a fluctuation can be attributed to nonuniformities of the measured devices, with special reference to the reproducibility of  $L_{\rm GS}$  values. For devices with  $L_{\rm GS} \sim 2~\mu{\rm m}$ , no breakdown was observed for voltages up to 100 V, which represents the limit of the power supply available during measurements.

This implies that breakdown voltages  $|V_{\rm BK}|$  well beyond 100 V can be obtained by simply setting an appropriate  $L_{\rm GS}$ . However, this parameter cannot be increased arbitrarily, in a tradeoff with other figures of merit requiring low  $L_{\rm GS}$  values to be optimized.

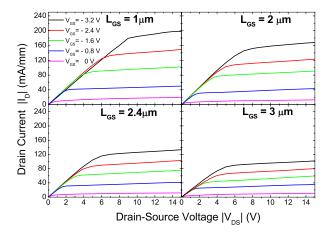

Fig. 6 shows the I-V characteristics of four device geometries, differing in  $L_{\rm GS}$ , but with a common  $L_{\rm DS}$  of 6.5  $\mu$ m.

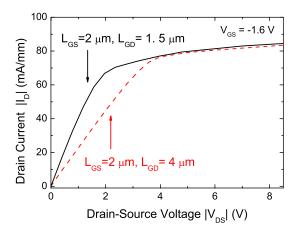

The dc characteristics confirm the above remarks, showing that the maximum output current density strongly depends on  $L_{\rm GS}$ . In particular, higher currents correspond to shorter  $L_{\rm GS}$  distances, as already noted in Fig. 2. Moreover, the slope of  $I_D$  versus  $V_{\rm DS}$  in the ohmic region (before the knee of each trace) is independent on  $L_{\rm GS}$  as expected. In addition, other conditions being equal, the knee voltage in the dc characteristics can be lowered by acting on  $L_{\rm GD}$ , which must be scaled down. This is demonstrated in Fig. 7, which shows

Fig. 6. Drain current density as a function of  $V_{\rm DS}$ , with  $V_{\rm GS}$  as a parameter, for several  $L_{\rm GS}$  values and  $L_{\rm DS}=6.5~\mu{\rm m}$ .

Fig. 7. Drain current density as a function of  $V_{DS}$ , for  $V_{GS} = -1.6$  V, with constant  $L_{GS}$  and two  $L_{GD}$  values.

how the slope of the  $I_D$ – $V_{DS}$  curve improves significantly by reducing  $L_{GD}$  from 4.0 to 1.5  $\mu$ m, while  $L_{GS}$  is held constant (2  $\mu$ m in this example). This can be explained by recalling that the saturated current of the two devices here considered must be approximately equal (since it depends on  $L_{GS}$  only in good approximation), while the saturated current regime will occur earlier in the device with shorter  $L_{GD}$  (due to the electric field in the gate–drain area increasing more rapidly).

As a consequence, the drain current of the device with  $L_{\rm GD}=1.5~\mu{\rm m}$  must reach the saturated value faster than the one with  $L_{\rm GD}=4~\mu{\rm m}$  as the drain voltage is increased.

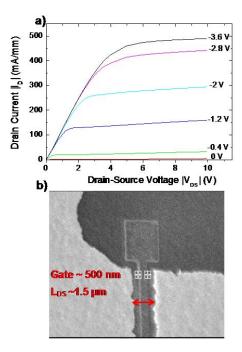

The results presented in this section constitute a valuable set of guidelines that, in addition to other well established rules, can help find the optimum tradeoff among often contrasting performance parameters. As an example, these results were used by the authors as a reference to optimize the geometry of a subsequent family of diamond-based MESFETs designed for RF operation. In particular, gate–source and gate–drain distances were minimized by setting  $L_{\rm DS}=1.5~\mu{\rm m}$  and centering the gate finger, whose length  $L_G$  was set to 0.5  $\mu{\rm m}$ .

Fig. 8(a) shows the measured dc curves of one such optimized device, whereas Fig. 8(b) shows a detail of the gate profile of the realized transistor. As it can be noted from the

Fig. 8. (a) Drain current density as a function of  $V_{\rm DS}$ , with  $V_{\rm GS}$  as a parameter, of an RF device with periphery  $2\times 50~\mu{\rm m}$  and  $L_G=L_{\rm GS}=L_{\rm GD}=0.5~\mu{\rm m}$ . (b) SEM picture of the channel geometry.

I-V graph, saturated drain current densities as high as about 500 mA/mm have been obtained.

### V. CONCLUSION

In this paper, the influence of gate–source and gate–drain distances on the diamond-based MESFET dc characteristics is investigated. The experimental results show that the scaling of the source–gate distance is a key factor for enhancing device performance, with positive consequences on both the output current density and device transconductance. In particular, with the decrease in  $L_{\rm GS}$  from 2 to 1  $\mu$ m, the value of  $g_m$  increases from 40 to 85 mS/mm. On the contrary, the device threshold voltage is almost independent of  $L_{\rm GS}$ .

In addition, the influence of the different gate position in a fixed drain–source channel has been demonstrated. An increase in the maximum drain current density  $I_D$  has been experimentally shown by shortening the gate–source distance.

However,  $L_{\rm GS}$  scaling affects the breakdown voltage of the device. For  $L_{\rm GS}\sim 1~\mu{\rm m}$ , the breakdown voltage was measured for different devices in the range 70–90 V.

Finally, keeping a constant gate–source distance, the knee voltage decreases by reducing the total length of the channel (drain–source distance).

The obtained results can be used as a design guideline for the layout of H-terminated diamond MESFETs with optimized performance.

### REFERENCES

- [1] J. E. Field, Properties of Diamond. London, U.K.: Academic, 1979.

- [2] J. F. Prins, "Applications of diamond films in electronics," in The Physics of Diamond, A. Paoletti and A. Tucciarone, Eds. Amsterdam, The Netherlands: IOS Press, 1997.

- [3] H. Kawarada, "Hydrogen-terminated diamond surfaces and interfaces," Surf. Sci. Rep., vol. 26, no. 7, pp. 205–206 and 208–259, 1996.

- [4] M. Kasu, K. Ueda, Y. Yamauchi, A. Tallaire, and T. Makimoto, "Diamond-based RF power transistors: Fundamentals and applications," *Diamond Rel. Mater.*, vol. 16, nos. 4–7, pp. 1010–1015, 2007.

- [5] V. Camarchia et al., "RF power performance evaluation of surface channel diamond MESFETs," Solid-State Electron., vol. 55, no. 1, pp. 19–24, 2011.

- [6] M. I. Landstrass and K. V. Ravi, "Resistivity of chemical vapor deposited diamond films," Appl. Phys. Lett., vol. 55, no. 10, pp. 975–977, 1989.

- [7] H. Kawarada, M. Aoki, and M. Ito, "Enhancement mode metal-semiconductor field effect transistors using homoepitaxial diamonds," Appl. Phys. Lett., vol. 65, no. 12, pp. 1563–1565, 1994.

- [8] H. Kawarada, "High-current metal oxide semiconductor field-effect transistors on H-terminated diamond surfaces and their high-frequency operation," *Jpn. J. Appl. Phys.*, vol. 51, no. 9R, p. 090111, 2012.

- [9] D. A. J. Moran, O. J. L. Fox, H. McLelland, S. Russell, and P. W. May, "Scaling of hydrogen-terminated diamond FETs to sub-100-nm gate dimensions," *IEEE Electron Device Lett.*, vol. 32, no. 5, pp. 599–601, May 2011.

- [10] M. Kasu, K. Ueda, H. Ye, Y. Yamauchi, S. Sasaki, and T. Makimoto, "High RF output power for H-terminated diamond FETs," *Diamond Rel. Mater.*, vol. 15, nos. 4–8, pp. 783–786, 2006.

- [11] M. Kasu et al., "Influence of epitaxy on the surface conduction of diamond film," Diamond Rel. Mater., vol. 13, no. 2, pp. 226–232, 2004.

- [12] A. Hiraiwa, A. Daicho, S. Kurihara, Y. Yokoyama, and H. Kawarada, "Refractory two-dimensional hole gas on hydrogenated diamond surface," *J. Appl. Phys.*, vol. 112, no. 12, pp. 124504-1–124504-6, Dec. 2012.

- [13] M. Kasu, H. Sato, and K. Hirama, "Thermal stabilization of hole channel on H-terminated diamond surface by using atomic-layer-deposited Al<sub>2</sub>O<sub>3</sub> overlayer and its electric properties," *Appl. Phys. Exp.*, vol. 5, no. 2, p. 025701, 2012.

- [14] D. Kueck, P. Leber, A. Schmidt, G. Speranza, and E. Kohn, "AlN as passivation for surface channel FETs on H-terminated diamond," *Diamond Rel. Mater.*, vol. 19, nos. 7–9, pp. 932–935, 2010.

- [15] D. Kueck, S. Jooss, and E. Kohn, "Technology of passivated surface channel MESFETs with modified gate structures," *Diamond Rel. Mater.*, vol. 18, no. 10, pp. 1306–1309, 2009.

- [16] P. Strobel, M. Riedel, J. Ristein, and L. Ley, "Surface transfer doping of diamond," *Nature*, vol. 430, pp. 439–441, Jun. 2004.

- [17] W. Chen, D. Qi, X. Gao, and A. T. S. Wee, "Surface transfer doping of semiconductors," *Prog. Surf. Sci.*, vol. 84, nos. 9–10, pp. 279–321, 2009.

- [18] S. A. O. Russell et al., "Surface transfer doping of diamond by MoO<sub>3</sub>: A combined spectroscopic and Hall measurement study," Appl. Phys. Lett., vol. 103, no. 20, p. 202112, 2013.

- [19] M. Kubovic and M. Kasu, "Enhancement and stabilization of hole concentration of hydrogen-terminated diamond surface using ozone adsorbates," *Jpn. J. Appl. Phys.*, vol. 49, no. 11R, p. 110208, 2010.

- [20] H. Matsudaira, S. Miyamoto, H. Ishizaka, H. Umezaawa, and H. Kawarada, "Over 20-GHz cutoff frequency submicrometer-gate diamond MISFETs," *IEEE Electron Device Lett.*, vol. 25, no. 7, pp. 480–482, Jul. 2004.

- [21] A. Aleksov, A. Denisenko, U. Spitzberg, T. Jenkins, W. Ebert, and E. Kohn, "RF performance of surface channel diamond FETs with sub-micron gate length," *Diamond Rel. Mater.*, vol. 11, nos. 3–6, pp. 382–386, 2002.

- [22] S. Russo and A. Di Carlo, "Influence of the source-gate distance on the AlGaN/GaN HEMT performance," *IEEE Trans. Electron Devices*, vol. 54, no. 5, pp. 1071–1075, May 2007.

- [23] X. Deng, B. Zhang, and Z. Li, "Two-dimensional analysis of the gate-source distance scaling effects in 4H-SiC MESFETs," Semicond. Sci. Technol., vol. 24, no. 1, p. 015011, 2009.

- [24] J. Khurgin, Y. J. Ding, and D. Jena, "Hot phonon effect on electron velocity saturation in GaN: A second look," *Appl. Phys. Lett.*, vol. 91, no. 25, pp. 252104-1–252104-3, Dec. 2007.

- [25] X. Zhou, F. Williams, and S. Albin, "Simulation of DC characteristics of nano-scale hydrogen-terminated diamond MISFETs," MRS Online Proc. Library, vol. 1551, p. 123, 2013.

- [26] I. Ciancaglioni et al., "Influence of the metallic contact in extremeultraviolet and soft X-ray diamond based Schottky photodiodes," J. Appl. Phys., vol. 110, no. 5, pp. 054513-1–054513-6, 2011.

- [27] P. Calvani et al., "K-band diamond MESFETs for RFIC technology," in Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC), Jun. 2009, pp. 355–358.

- [28] P. Calvani et al., "Diamond MESFET technology development for microwave integrated circuits," in Proc. 4th Eur. Microw. Integr. Circuits Conf. (EuMIC), Rome, Italy, Sep. 2009, pp. 148–151.

- [29] M. C. Rossi et al., "RF power performance of submicron MESFET on hydrogen terminated polycrystalline diamond," in Proc. Int. Semiconductor Device Res. Symp. (ISDRS), College Park, MD, USA, Dec. 2009, pp. 1–2.

- [30] R. Chu, Y. Zhou, J. Liu, D. Wang, K. J. Chen, and K. M. Lau, "AlGaN-GaN double-channel HEMTs," *IEEE Trans. Electron Devices*, vol. 52, no. 4, pp. 438–446, Apr. 2005.

- [31] A. Kamath et al., "Double-channel AlGaN/GaN high electron mobility transistor with back barriers," IEEE Electron Device Lett., vol. 33, no. 12, pp. 1690–1692, Dec. 2012.

- [32] K. Tsugawa, H. Umezawa, and H. Kawarada, "Characterization of diamond surface-channel metal-semiconductor field-effect transistor with device simulation," *Jpn. J. Appl. Phys.*, vol. 40, no. 5A, p. 3101, 2001.

- [33] C. E. Nebel and J. Ristein, Thin-Film Diamond II Semiconductors and Semimetals, vol. 77. Amsterdam, The Netherlands: Academic, 2004.

Claudio Verona received the Physics Degree from the Sapienza University of Rome, Rome, Italy, and the Ph.D. degree in microsystems engineering from the Università di Roma Tor Vergata, Rome, in 2010.

His current research interests include the design, fabrication, modeling, and testing of micro-devices based on diamond for different applications, i.e., UV/X detectors, dosimeters, and transistors.

Walter Ciccognani received the M.S. degree in electronics engineering and the Ph.D. degree in telecommunications and microelectronics from the Università di Roma Tor Vergata, Rome, Italy, in 2002 and 2007, respectively.

He has been an Assistant Professor with the Università di Roma Tor Vergata since 2012, where he has been teaching the course in microwave measurements since 2013.

Sergio Colangeli received the M.S. degree in electronics engineering and the Ph.D. degree in telecommunications and microelectronics from the Università di Roma Tor Vergata, Rome, Italy, in 2008 and 2013, respectively.

His current research interests include low-noise design methodologies for microwave applications and noise characterization/modeling of microwave active devices.

Fabio Di Pietrantonio received the Degree in electronics engineering and the Ph.D. degree in microsystems engineering from the Università di Roma Tor Vergata, Rome, Italy, in 2003 and 2007, respectively.

He was appointed as a Researcher with the National Research Council—Istituto di Acustica e Sensoristica O.M. Corbino, Rome, in 2010.

**Ennio Giovine** received the Ph.D. degree in physics from the Università di Roma Tor Vergata, Rome, Italy.

He is currently a Staff Researcher with the National Research Council—Istituto di Fotonica e Nanotecnologie, Rome. He is involved in high-power and high-frequency GaAs and GaN devices, nanoelectronics devices, microelectromechanical systems, and terahertz detectors. He has authored about 80 reviewed papers.

Marco Marinelli is currently a Full Professor of Physics with the Department of Industrial Engineering, Università di Roma Tor Vergata, Rome, Italy. His current research interests include the growth and characterization of chemical vapor deposited diamond

Prof. Marinelli received the scholarship from the Hyogo Foundation for Science and Technology at the Department of Electronic Engineering, University of Osaka, Osaka, Japan, in 1995.

**Ernesto Limiti** has been a Full Professor of Electronics with the Faculty of Engineering, Università di Roma Tor Vergata, Rome, Italy, since 2002. His current research interests include the microwave and millimetre-wave electronics area.

**Gianluca Verona-Rinati** received the Degree in physics and the Ph.D. degree in microsystem engineering from the Università di Roma Tor Vergata, Rome, Italy, in 1996 and 2000, respectively.

He is currently an Assistant Professor with the Department of Industrial Engineering, Università di Roma Tor Vergata. His current research interests include the growth and characterization of synthetic diamond for sensors application.